Product information presented is for internal use within AAT Inc. only. Details are subject to change without notice.

## MULTI-CHANNEL POWER SUPPLY FOR TFT LCD PANELS BOOST, BUCK, CHARGE PUMPS, GPM, OP AMP, GAMMA REFERENCE, RESET

## **FEATURES**

- 8V to 14V Input Supply Voltage Range

- 500kHz/750kHz Selectable Frequency

- Current Mode Boost Regulator

- Built-In 20V, 3.6A, 0.1Ω N-MOSFET

- ♦ Fast Load Transient Response

- Adjustable Soft-Start

- Adjustable Current Limit

- External PMOS Gate Control for AVDD Sequencing

- Current Mode Buck Regulator

- Built-in 16.5V, 3.2A, 0.1Ω, MOSFET

- ♦ Fast Load Transition Response

- Internal Soft-Start and Compensation

- Positive Charge Pump Regulator

- Negative Charge Pump Regulator

- High Voltage Switch with Gate Pulse Modulation

- Adjustable Power On Delay Time

- Operational Amplifier for VCOM Buffer

- ±200mA Short-Circuit Current

- ♦ 45V/µs Slew Rate

- High Accuracy LDO for Gamma Reference

- ◆ ±1% Adjustable Output Voltage

- ♦ Up to 60mA Load Current

- RESET (XAO Voltage Detector)

- Adjustable Detecting Voltage

- N-Channel Open-Drain Output

- Protection

- Input Under-Voltage Lockout (UVLO)

- Overload Current Protection (OCP)

- Over Voltage Protection (OVP)

- Short Circuit Protection (SCP)

- Under Voltage Protection (UVP)

- Thermal Shutdown (OTP)

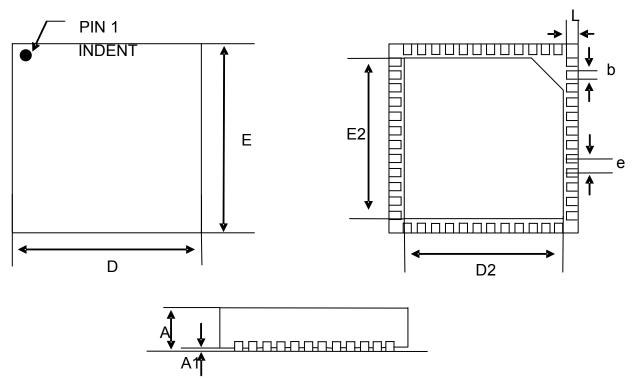

- WQFN 48-7x7x0.75 Package

**APPLICATIONS**

### LCD TV Panel

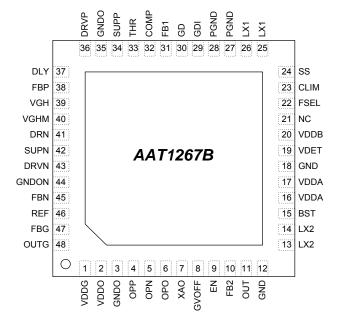

## **PIN CONFIGURATION**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 1.01

Page 1 of 30

September 2016

## **GENERAL DESCRIPTION**

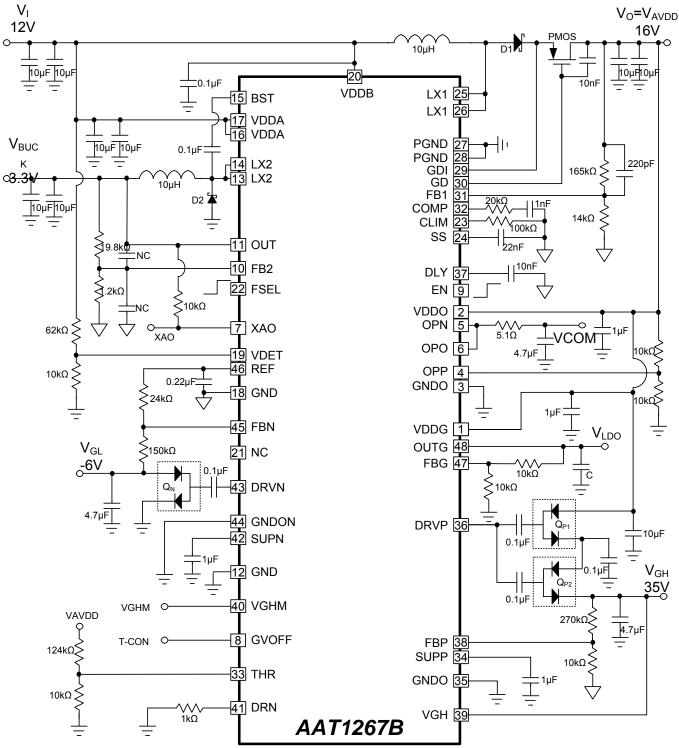

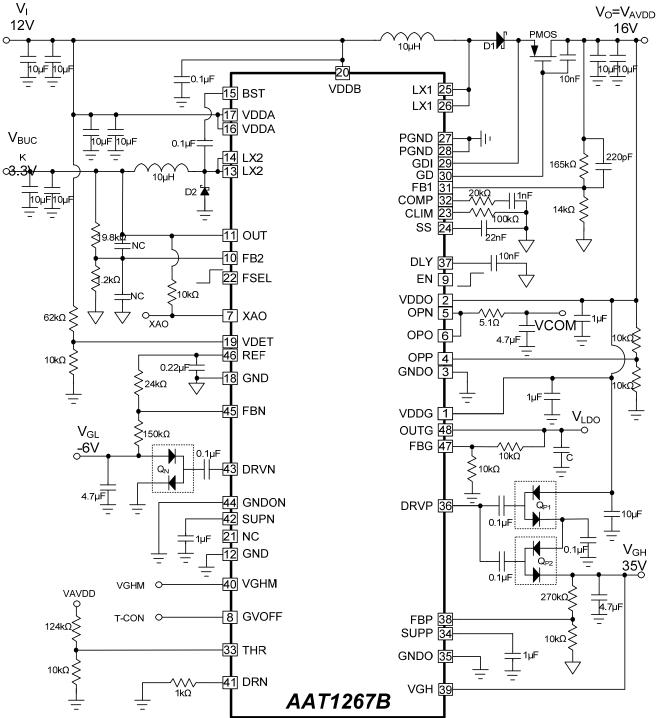

The AAT1267B offers a compact power supply solution to provide all voltages required by a thin-film-transistor (TFT) liquid-crystal display (LCD) panel for TV applications running from a 12V supply rail. It includes a boost and a buck regulator, a positive and a negative regulated charge-pump, a high voltage switch with gate pulse modulation, an operational amplifier, a high accuracy LDO for gamma reference and one open drain RESET output.

The current mode boost regulator provides a fast transient response supply voltage for the source drivers. It provides an output voltage up to 20V from input voltages ranging from 8V to 14V. The boost regulator integrates a low  $R_{DSON}$  (0.1 $\Omega$ ) N-MOSFET, and operates at a selectable switching frequency of either 500kHz or 750kHz, thereby minimizing board space while providing good efficiency. An externally programmed soft start minimizes inrush current and output overshoot. In addition, the AAT1267B integrates a control block that can drive an external P-Channel MOSFET to sequence power to source drivers.

The current mode buck regulator operates at either 500kHz or 750kHz and typically supplies system logic power (T-CON). It provides fast load transient response to pulsed loads while producing efficiencies over 90%. This buck regulator integrates a 16.5V, 3.2A, 0.1 $\Omega$ , power MOSFET that allows the use of ultra-small inductors and ceramic capacitors. A built-in 7-bit digital soft-start function controls startup inrush currents.

## AAT1267B

The positive and negative charge pump regulators provide supply voltages for the TFT LCD's gate drivers. Both output voltages can be adjusted with external resistive voltage dividers. For improving TFT LCD image quality, a gate pulse modulation (GPM) circuit shapes the gate-on signal. The slope of the gate-on voltage and GPM power on delay time can be set by external resistor and capacitor.

The operational amplifier drives the LCD backplane (VCOM). This unity-gain buffer is capable of rail-to-rail input and output,  $\pm 200$ mA output short-circuit current, and a 45V/µs slew rate.

A high accuracy low dropout linear regulator is used as an adjustable reference voltage for gamma correction. The LDO guarantees a minimum 60mA output current, and has an internal high accuracy reference of +/-0.5%. The LDO output is set via external feedback resistors.

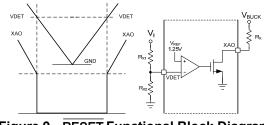

The RESET function is used to monitor the device supply voltage. A reset signal is issued via an open drain NMOS when the supply is below a programmable threshold. The threshold is set by external resistors and the delay time is set by an external capacitor.

The AAT1267B device includes various protection features such as UVLO, OCP, OVP, SCP, UVP and thermal shutdown.

The AAT1267B is available in a small 7x7x0.75mm, ultra-thin, 48 pin QFN package with a bottom side exposed thermal pad to provide optimal heat dissipation. The device is rated to operate from  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient temperature range.

## **ORDERING INFORMATION**

| DEVICE<br>TYPE | PART NUMBER    | PACKAGE            | PACKING             | TEMP.<br>RANGE   | MARKING                    | MARKING<br>DESCRIPTION                                       |

|----------------|----------------|--------------------|---------------------|------------------|----------------------------|--------------------------------------------------------------|

| AAT1267B       | AAT1267B-Q51-T | Q51:WQFN<br>48-7*7 | T: Tape<br>and Reel | –40 °C to +85 °C | AAT1267B<br>XXXXXX<br>XXXX | Device Type<br>Lot no. (6~9 Digits)<br>Date Code. (4 Digits) |

Note: All AAT products are lead free and halogen free.

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Page 2 of 30

Version 1.01

September 2016

### **AAT1267B**

**TYPICAL APPLICATION**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 3 of 30

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                                             | SYMBOL               | VALUE                          | UNIT |

|---------------------------------------------------------------------------------------|----------------------|--------------------------------|------|

| VDDA, VDDB, SUPN, EN, FSEL to GND                                                     | V <sub>IN</sub>      | -0.3 to +16.5                  | V    |

| PGND, GNDO, GNDON to GND                                                              | V <sub>IN</sub>      | -0.3 to +0.3                   | V    |

| SUPP, GDI, GD, VDDO, OPP, OPN, VDDG, BST to GND                                       | V <sub>H1</sub>      | -0.3 to +20                    | V    |

| LX1 to PGND                                                                           | V <sub>H2</sub>      | -0.3 to +20                    | V    |

| LX2 to GND                                                                            | V <sub>H3</sub>      | –0.3 to (V <sub>IN</sub> +0.3) | V    |

| VGHM, VGH, DRN to GND                                                                 | V <sub>H4</sub>      | -0.3 to +40.0                  | V    |

| VGH to VGHM                                                                           | V <sub>H5</sub>      | -0.3 to +40.0                  | V    |

| VGH, VGHM to DRN                                                                      | V <sub>H6</sub>      | -0.3 to +40.0                  | V    |

| FB1, FB2, FBP, FBN, XAO, VDET, GVOFF, CLIM, SS, COMP, THR, DLY1, REF, FBG, OUT to GND | V <sub>I1</sub>      | -0.3 to +6.5                   | V    |

| Output Voltage1 (DRVP to GNDO)                                                        | V <sub>01</sub>      | –0.3 to (V <sub>H1</sub> +0.3) | V    |

| Output Voltage2 (DRVN to GNDON)                                                       | V <sub>O2</sub>      | –0.3 to (V <sub>IN</sub> +0.3) | V    |

| Output Voltage3 (OPO to GNDO)                                                         | V <sub>O3</sub>      | –0.3 to (V <sub>H1</sub> +0.3) | V    |

| Output Voltage4 (OUTG to GND)                                                         | V <sub>O4</sub>      | –0.3 to (V <sub>H1</sub> +0.3) | V    |

| Operating Ambient Temperature Range                                                   | T <sub>c</sub>       | -40 to +85                     | °C   |

| Operating Junction Temperature Range                                                  | TJ                   | -40 to +150                    | °C   |

| Storage Temperature Range                                                             | T <sub>STORAGE</sub> | -65 to +150                    | °C   |

| Package Thermal Range                                                                 | θ <sub>JA</sub>      | 29                             | °C   |

| Power Dissipation @ $T_c$ = +25 °C , $T_J$ = +125 °C                                  | P <sub>d</sub>       | 3.448                          | W    |

| ESD Susceptibility Human Body Mode                                                    | HBM                  | 2k                             | V    |

| ESD Susceptibility Machine Mode                                                       | MM                   | 200                            | V    |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the devices. Exposure to ABSOLUTE MAXIMUM RATINGS conditions for extended periods may affect device reliability.

Page 4 of 30

Version 1.01

# **ELECTRICAL CHARACTERISTICS**

(V\_{IN} = V\_{DDA} = V\_{DDB} = 12V, T\_C = +25  $^{\circ}\text{C}$  , unless otherwise specified.)

### General

| PARAMETER                         | SYMBOL            | TEST CONDITION                     | MIN | TYP | MAX | UNIT |

|-----------------------------------|-------------------|------------------------------------|-----|-----|-----|------|

| VDDA, VDDB Input Voltage<br>Range | V <sub>DD</sub>   |                                    | 8   | 12  | 14  | V    |

| VDDA, VDDB Quiescent Current      | Ι <sub>Q</sub>    | LX not Switching                   | -   | 5   | -   | mA   |

| Under-Voltage Lockout Threshold   | V <sub>UVLO</sub> | V <sub>IN</sub> Rising             | 6   | 7   | 8   | V    |

| Under-Voltage Lockout Threshold   |                   | V <sub>IN</sub> Falling Hysteresis | 0.1 | 0.3 | 0.5 | V    |

| Switching Frequency               |                   | FSEL = V <sub>IN</sub>             | 630 | 750 | 870 | kHz  |

| Switching Frequency               | f <sub>OSC</sub>  | FSEL = GND                         | 420 | 500 | 580 | kHz  |

| Thermal Shutdown Threshold        | T <sub>SHDN</sub> | Falling Edge                       | -   | 160 | -   | °C   |

### **Boost Regulator**

| PARAMETER                         | SYMBOL                | TEST CONDITION                      | MIN             | ТҮР    | MAX    | UNIT |

|-----------------------------------|-----------------------|-------------------------------------|-----------------|--------|--------|------|

| Output Voltage Range              | -                     |                                     | V <sub>IN</sub> | _      | 18     | V    |

| FB1 Regulation Voltage            | $V_{\text{FB1}}$      |                                     | 1.2375          | 1.2500 | 1.2625 | V    |

| FB1 Input Leakage Current         | I <sub>Leak1</sub>    | V <sub>FB1</sub> = 1.25v            | -40             | 0      | +40    | nA   |

| FB1 Line Regulation               | -                     | 10.8V< V <sub>IN</sub> <13.2V       | -               | 0.08   | -      | %V   |

| FB1 Load Regulation               | -                     | 0< I <sub>LOAD</sub> < Full         | -               | 0.5    | -      | %    |

| LX1 Current Limit                 | I <sub>LIM1</sub>     | $R_{CLIM} > 50 k\Omega$ or Floating | 3.0             | 3.6    | -      | А    |

| LX1 ON-Resistance                 | R <sub>ON_LX1</sub>   |                                     | -               | 150    | 300    | mΩ   |

| LX1 Leakage Current               | I <sub>Leak2</sub>    |                                     | -               | 0.01   | 5.00   | μA   |

| Maximum Duty Cycle                | -                     |                                     | 70              | 80     | 85     | %    |

| FB1 SCP Trip Level                | V <sub>S1</sub>       | Falling Edge                        | 0.45            | 0.50   | 0.55   | V    |

| FB1 UVP Level                     | $V_{F1}$              | Falling Edge                        | 0.96            | 1.00   | 1.04   | V    |

| Duration to Trigger UVP Condition | t <sub>F1</sub>       |                                     | -               | 50     | -      | ms   |

| Internal Soft-Start Time          | t <sub>ss1</sub>      | C <sub>SS</sub> < 220pf             | -               | 16     | -      | ms   |

| SS Charge Current                 | I <sub>SS</sub>       | C <sub>SS</sub> > 220pf             | 4               | 5      | 6      | μA   |

| Transconductance                  | <b>g</b> <sub>m</sub> |                                     | 70              | 105    | 240    | μS   |

| Voltage Gain                      | A <sub>V</sub>        |                                     | -               | 1,400  | -      | V/V  |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 5 of 30

# **ELECTRICAL CHARACTERISTICS**

(V\_{IN} = V\_{DDA} = V\_{DDB} = 12V, T\_C = +25  $^{\circ}$  C , unless otherwise specified.)

### **Buck Regulator**

| PARAMETER                                | SYMBOL              | TEST CONDITION                | MIN    | TYP    | MAX    | UNIT |

|------------------------------------------|---------------------|-------------------------------|--------|--------|--------|------|

| Output Voltage Range                     | -                   |                               | 1.5    | -      | 5.0    | V    |

| OUT Voltage in Fixed Mode                | $V_{FB33}$          | FB2 = GND                     | 3.267  | 3.300  | 3.333  | V    |

| FB2 Voltage in Adjustable Mode           | $V_{\text{FB2}}$    |                               | 1.2375 | 1.2500 | 1.2625 | V    |

| FB2 Input Leakage Current                | I <sub>Leak3</sub>  |                               | -40    | 0      | +40    | nA   |

| FB2 Line Regulation                      | -                   | 10.8V< V <sub>IN</sub> <13.2V | -      | 0.1    | -      | %/V  |

| FB2 Load Regulation                      | -                   | 0 < I <sub>LOAD</sub> < 2A    | -      | 0.5    | -      | %/A  |

| LX2 Current Limit                        | I <sub>LIM2</sub>   |                               | 2.5    | 3.2    | -      | А    |

| LX2 to VDDA NMOS Switch<br>ON-Resistance | R <sub>ON_LX2</sub> |                               | -      | 100    | 200    | mΩ   |

| Maximum Duty Cycle                       | -                   |                               | 70     | 80     | 85     | %    |

| FB2 SCP Trip Level                       | $V_{S2}$            | Falling Edge                  | 0.45   | 0.5    | 0.55   | V    |

| FB2 UVP Trip Level                       | $V_{F2}$            | Falling Edge                  | 0.96   | 1.00   | 1.04   | V    |

| Duration to Trigger UVP Condition        | t <sub>F2</sub>     |                               | -      | 50     | -      | ms   |

| Internal Soft-Start Time                 | t <sub>SS2</sub>    |                               | -      | 3      | -      | ms   |

### **Positive Charge Pump Regulator**

| PARAMETER                              | SYMBOL             | TEST CONDITION                | MIN   | ТҮР   | MAX   | UNIT |

|----------------------------------------|--------------------|-------------------------------|-------|-------|-------|------|

| FBP Regulation Voltage                 | $V_{FBP}$          |                               | 1.225 | 1.250 | 1.275 | V    |

| FBP Input Leakage Current              | I <sub>Leak4</sub> | V <sub>FBP</sub> = 1.25V      | -40   | 0     | +40   | nA   |

| FBP Line Regulation Error              | -                  | 10.8V< V <sub>IN</sub> <13.2V | -     | -     | 6     | mV   |

| DRVN P-MOSFET<br>ON-Resistance         | R <sub>ON_P3</sub> |                               | -     | 4     | -     | Ω    |

| DRVP N-MOSFET<br>ON-Resistance         | R <sub>ON_N3</sub> |                               | -     | 1     | -     | Ω    |

| FBP SCP Trip Level                     | $V_{S3}$           | Falling Edge                  | 0.45  | 0.50  | 0.55  | V    |

| FBP UVP Trip Level                     | $V_{F3}$           | Falling Edge                  | 0.96  | 1.00  | 1.04  | V    |

| Duration to Trigger Fault<br>Condition | t <sub>F3</sub>    |                               | -     | 50    | -     | ms   |

| Internal Soft-Start Time               | t <sub>SS3</sub>   |                               | -     | 3     | -     | ms   |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 6 of 30

# **ELECTRICAL CHARACTERISTICS**

(V\_{IN} = V\_{DDA} = V\_{DDB} = 12V, T\_C = +25  $^{\circ}$  C , unless otherwise specified.)

### Negative Charge Pump Regulator

| PARAMETER                              | SYMBOL             | TEST CONDITION                | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------|--------------------|-------------------------------|------|------|------|------|

| FBN Regulation Voltage                 | $V_{FBN}$          |                               | 0.21 | 0.25 | 0.29 | V    |

| FBN Input Leakage Current              | I <sub>Leak5</sub> | V <sub>FBN</sub> = 0.25V      | -40  | 0    | +40  | nA   |

| FBN Line Regulation Error              | -                  | 10.8V< V <sub>IN</sub> <13.2V | -    | -    | 6    | mV   |

| DRVN P-MOSFET<br>ON-Resistance         | R <sub>ON_P4</sub> |                               | -    | 4    | -    | Ω    |

| DRVN N-MOSFET<br>ON-Resistance         | R <sub>ON_N4</sub> |                               | -    | 1    | -    | Ω    |

| FBN SCP Trip Level                     | $V_{S4}$           | Falling Edge                  | 0.80 | 0.85 | 0.90 | V    |

| FBN UVP Trip Level                     | $V_{F4}$           | Falling Edge                  | 0.40 | 0.45 | 0.50 | V    |

| Duration to Trigger Fault<br>Condition | t <sub>F4</sub>    |                               | -    | 50   | -    | ms   |

| Internal Soft-Start Time               | t <sub>SS4</sub>   |                               | _    | 3    | -    | ms   |

### High Voltage Switch with Gate Pulse Modulation

| PARAMETER                                  | SYMBOL             | TEST CONDITION | MIN | TYP | MAX | UNIT |

|--------------------------------------------|--------------------|----------------|-----|-----|-----|------|

| GVOFF Input Low Voltage                    | V <sub>IH</sub>    |                | -   | -   | 0.6 | V    |

| GVOFF Input High Voltage                   | V <sub>IL</sub>    |                | 1.5 | -   | 5.5 | V    |

| GVOFF Input Current                        | I <sub>Leak6</sub> |                | -40 | 0   | +40 | nA   |

| GVOFF to VGHM Rising<br>Propagation Delay  | t <sub>RP</sub>    |                | -   | 100 | -   | ns   |

| GVOFF to VGHM Falling<br>Propagation Delay | t <sub>FP</sub>    |                | -   | 250 | -   | ns   |

| VGH Input Voltage Range                    | V <sub>IGH</sub>   |                | -   | -   | 40  | V    |

| VGHM to VGH Switch<br>On-Resistance        | R <sub>ON_P5</sub> |                | -   | 5   | 10  | Ω    |

| VGHM to DRN Switch<br>On-Resistance        | R <sub>ON_P6</sub> |                | -   | 40  | 60  | Ω    |

| THR to VGHM Voltage Gain                   |                    |                | -   | 10  | -   | V/V  |

| DLY Charge Current                         | I <sub>DLY</sub>   |                | 5   | 7   | 9   | μA   |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 7 of 30

# **ELECTRICAL CHARACTERISTICS**

(V\_{IN} = V\_{DDA} = V\_{DDB} = 12V, T\_C = +25  $^{\circ}$  C , unless otherwise specified.)

### **Operational Amplifier for VCOM Buffer**

| PARAMETER                 | SYMBOL             | TEST CONDITION                              | MIN          | ТҮР          | MAX          | UNIT |

|---------------------------|--------------------|---------------------------------------------|--------------|--------------|--------------|------|

| VDDO Input Voltage Range  | V <sub>OPI</sub>   |                                             | 8            | -            | 18           | V    |

| VDDO Supply Current       | I <sub>OP</sub>    |                                             | -            | 1.5          | -            | mA   |

| Input Offset Voltage      | V <sub>os</sub>    |                                             | -            | -            | 20           | mV   |

| Output Voltage Swing High | V <sub>он</sub>    | I <sub>OPO</sub> = 10mA                     | VDDO<br>-300 | VDDO<br>-100 | -            | mV   |

| Output Voltage Swing Low  | V <sub>OL</sub>    | I <sub>OPO</sub> = -10mA                    | -            | VDDO<br>+100 | VDDO<br>+300 | mV   |

| Short Circuit Current     | I <sub>SHORT</sub> | OPO = OPN,<br>OPP = 1/2 * V <sub>AVDD</sub> | -            | ±200         | -            | mA   |

| –3dB Bandwidth            | f_ <sub>3dB</sub>  | $R_L = 10k\Omega, C_L = 10pF$               | -            | 20           | -            | MHz  |

| Slew Rate                 | SR                 |                                             | -            | 45           | -            | V/µs |

### High Accuracy LDO for Gamma Reference

| PARAMETER                 | SYMBOL             | TEST CONDITION           | MIN    | ТҮР    | MAX    | UNIT |

|---------------------------|--------------------|--------------------------|--------|--------|--------|------|

| VDDG Input Voltage Range  | V <sub>OPI</sub>   |                          | 10     | -      | 18     | V    |

| Quiescent Current         | Ι <sub>Q</sub>     |                          | -      | 125    | 250    | μA   |

| FBG Feedback Voltage      | $V_{FBG}$          |                          | 1.2375 | 1.2500 | 1.2625 | V    |

| FBG Input Leakage Current | I <sub>Leak7</sub> | V <sub>FBG</sub> = 1.25V | -40    | 0      | +40    | nA   |

| Output Current Limit      | I <sub>LIM3</sub>  |                          | 60     | -      | -      | mA   |

| Dropout Voltage           | V <sub>DROP</sub>  | I <sub>LOAD</sub> = 60mA | -      | 0.5    | -      | V    |

### **RESET** (XAO Voltage Detector)

| PARAMETER                  | SYMBOL             | TEST CONDITION           | MIN    | TYP    | MAX    | UNIT |

|----------------------------|--------------------|--------------------------|--------|--------|--------|------|

| VDET Detecting Voltage     | $V_{\text{DET}}$   | Falling Edge             | 1.2375 | 1.2500 | 1.2625 | V    |

| VDET Input Leakage Current | I <sub>Leak8</sub> | V <sub>DET</sub> = 1.25V | -40    | 0      | +40    | nA   |

| XAO Output Voltage         | $V_{XAO}$          | V <sub>DET</sub> = GND   | -      | -      | 0.4    | V    |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 8 of 30

# **ELECTRICAL CHARACTERISTICS**

(V\_{IN} = V\_{DDA} = V\_{DDB} = 12V, T\_C = +25  $^{\circ}\text{C}$  , unless otherwise specified.)

### Reference

| PARAMETER                 | SYMBOL           | TEST CONDITION              | MIN    | TYP    | MAX    | UNIT |

|---------------------------|------------------|-----------------------------|--------|--------|--------|------|

| Reference Output Voltage  | $V_{REF}$        | No External Load            | 1.2375 | 1.2500 | 1.2625 | V    |

| Reference Load Regulation | -                | 0 < I <sub>REF</sub> < 50μA | -      | -      | 5      | mV   |

| Reference Sink Current    | I <sub>REF</sub> | REF in Regulation           | 10     | -      | -      | μA   |

### **Sequence Control**

| PARAMETER               | SYMBOL           | TEST CONDITION                    | MIN | ТҮР                | MAX             | UNIT |

|-------------------------|------------------|-----------------------------------|-----|--------------------|-----------------|------|

| GD Output Sink Current  | $I_{GD}$         | EN = High, VGDI = V <sub>IN</sub> | -   | 10                 | -               | μA   |

| GD ON Voltage           | $V_{GD}$         | EN = High, VGDI = V <sub>IN</sub> | -   | V <sub>IN</sub> -5 | -               | V    |

| EN Input High Voltage   | $V_{\text{ENH}}$ |                                   | 1.5 | -                  | V <sub>IN</sub> | V    |

| EN Input Low Voltage    | $V_{\text{ENL}}$ |                                   | -   | -                  | 0.6             | V    |

| EN Pull-Down Resistance | R <sub>EN</sub>  |                                   | -   | 1                  | -               | MΩ   |

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 1.01

Page 9 of 30

| <b>PIN DESCRIPTIO</b> | Ν |

|-----------------------|---|

|-----------------------|---|

| PIN NO. | NAME  | I/O | DESCRIPTION                                                           |

|---------|-------|-----|-----------------------------------------------------------------------|

| 1       | VDDG  | Ι   | Gamma Reference LDO Power Supply Input                                |

| 2       | VDDO  | Ι   | Operational Amplifier Power Supply Input                              |

| 3       | GNDO  | -   | Operational Amplifier Power Ground                                    |

| 4       | OPP   | I   | Operational Amplifier Inverting Input                                 |

| 5       | OPN   | I   | Operational Amplifier Non-inverting Input                             |

| 6       | OPO   | 0   | Operational Amplifier Output                                          |

| 7       | XAO   | 0   | RESET Function Output                                                 |

| 8       | GVOFF | Ι   | High Voltage Switch with Gate Pulse Modulation Logic Control Input    |

| 9       | EN    | I   | Enable Input                                                          |

| 10      | FB2   | Ι   | Buck Regulator Feedback Input                                         |

| 11      | OUT   | 0   | Buck Regulator Output Sense Pin                                       |

| 12      | GND   | -   | Analog GND                                                            |

| 13      | LX2   | 0   | Buck Regulator Switching Node                                         |

| 14      | LX2   | 0   | Buck Regulator Switching Node                                         |

| 15      | BST   | Ι   | Buck Regulator Bootstrap Capacitor Connection                         |

| 16      | VDDA  | Ι   | Buck Regulator Power Supply Input                                     |

| 17      | VDDA  | I   | Buck Regulator Power Supply Input                                     |

| 18      | GND   | -   | Analog GND                                                            |

| 19      | VDET  | Ι   | Voltage Detection Input (RESET Function)                              |

| 20      | VDDB  | Ι   | Internal 5V Linear Regulator and Startup Circuitry Power Supply Input |

| 21      | NC    | -   | Not Connected                                                         |

| 22      | FSEL  | Ι   | Frequency Select Pin                                                  |

| 23      | CLIM  | I   | Adjustable Boost Current Limit Pin                                    |

| 24      | SS    | Ι   | Soft-Start Time Setting Pin                                           |

| 25      | LX1   | 0   | Boost Regulator Switching Node                                        |

| 26      | LX1   | 0   | Boost Regulator Switching Node                                        |

| 27      | PGND  | -   | Boost Regulator Power Ground                                          |

- 台灣類比科技股份有限公司 -

\_

Advanced Analog Technology, Inc. –

Version 1.01

Page 10 of 30

**PIN DESCRIPTION**

| PIN NO. | NAME  | I/O | DESCRIPTION                                                                 |

|---------|-------|-----|-----------------------------------------------------------------------------|

| 28      | PGND  | -   | Boost Regulator Power Ground                                                |

| 29      | GDI   | Ι   | Boost Regulator Output Sense Pin                                            |

| 30      | GD    | 0   | External PMOS Gate Control for Boost Regulator Sequencing                   |

| 31      | FB1   | I   | Boost Regulator Feedback Input                                              |

| 32      | COMP  | I   | Boost Regulator Compensation Pin                                            |

| 33      | THR   | I   | VGHM Falling Regulation Setting Pin                                         |

| 34      | SUPP  | I   | Positive Charge Pump Regulator Power Supply Input                           |

| 35      | GNDO  |     | VGH Charge Pump Ground                                                      |

| 36      | DRVP  | 0   | VGH Charge Pump Regulator Output                                            |

| 37      | DLY   | I   | High Voltage Switch with Gate Pulse Modulation (GPM) Delay Time Setting Pin |

| 38      | FBP   | Ι   | VGH Charge-Pump Regulator Feedback Input                                    |

| 39      | VGH   | I   | High Voltage Switch with GPM Power Supply Input                             |

| 40      | VGHM  | 0   | High Voltage Switch with GPM Output                                         |

| 41      | DRN   | 0   | High Voltage Switch with GPM Discharge Setting pin                          |

| 42      | SUPN  | I   | Negative Charge Pump Regulator Power Supply Input                           |

| 43      | DRVN  | 0   | Negative Charge Pump Regulator Output                                       |

| 44      | GNDON |     | VGL Charge Pump Ground                                                      |

| 45      | FBN   | I   | Negative Charge Pump Regulator Feedback Input                               |

| 46      | REF   | 0   | Reference Output                                                            |

| 47      | FBG   | I   | Gamma Reference LDO Feedback Input                                          |

| 48      | OUTG  | 0   | Gamma Reference LDO Output                                                  |

| 49      | EP    |     | Exposed PAD                                                                 |

Advanced Analog Technology, Inc. – Version 1.01

Page 11 of 30

September 2016

### **AAT1267B**

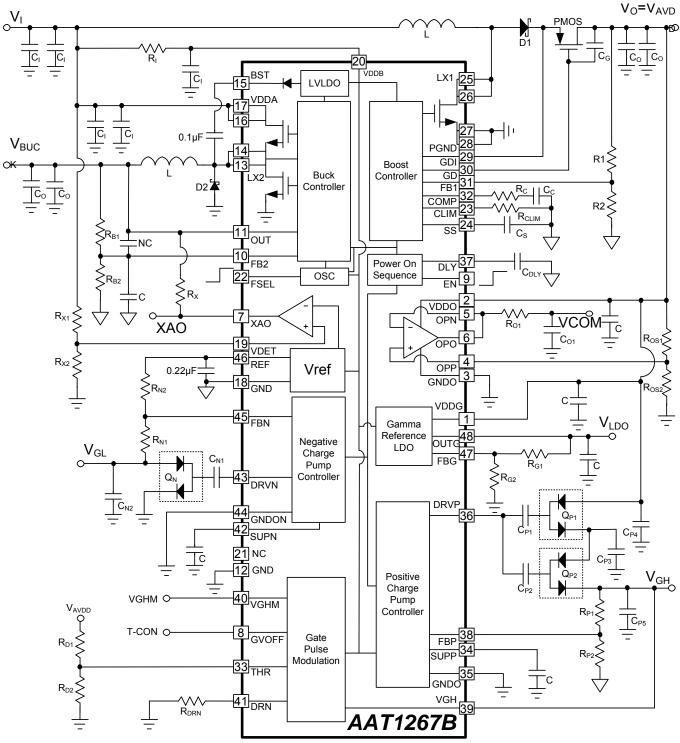

## **FUNCTION BLOCK DIAGRAM**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 1.01

Page 12 of 30

September 2016

### **AAT1267B**

## **TYPICAL APPLICATION CIRCUIT**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 13 of 30

## **THEORY OF OPERATION**

The AAT1267B offers a complete solution for powering TFT LCD panels. The device integrates a boost regulator for the source driver, a buck regulator for the system logic power supply, a positive charge pump regulator for the gate-on driver, a negative charge pump regulator for gate-off, a high voltage switch with gate pulse modulation for flicker compensation, an operational amplifier for supplying the LCD backplane VCOM, a high accuracy high-voltage LDO for gamma reference and various system protection schemes such as soft start, power up sequencing, fault protection, thermal shutdown, and supervisory reset.

### **Boost Regulator**

The boost regulator uses a peak current mode control scheme that provides fast output response during transients, and also simple compensation. With an integrated low  $R_{DSON}$  (typical 0.1 $\Omega$ ) NMOS, user controlled soft start, and selectable switching frequency of either 500kHz or 750kHz, this boost regulator is a compact and economical solution but also provides design in flexibility. The boost regulator operates from a minimum input voltage of 8V, and delivers an output voltage by modulating duty cycle D of the internal power NMOS in each switching cycle. The duty cycle is calculated by

$$D = \frac{V_O - V_I}{V_O} \quad \text{or} \ \frac{V_O}{V_I} = \frac{1}{1 - D}, \quad \left(V_O = V_{AVDD}\right)$$

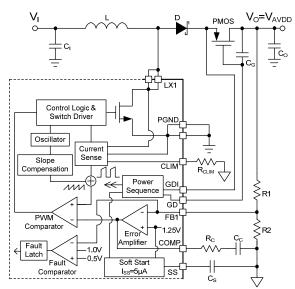

where  $V_O (V_{AVDD})$  is the output of the boost regulator. At the heart of the current mode topology are two feedback loops. See the AAT1267B Boost Regulator Functional Block Diagram Figure 1. One feedback loop generates a ramp voltage as the inductor current flows through the on resistance of the internal power switch. The second loop monitors the boost output via a resistive divider to the FB1 pin and compares the FB1 voltage to an internal reference voltage of 1.25V using a transconductance error amp. Regulation is achieved by modulating the internal power switch ON time. The

### AAT1267B

modulating duty cycle is determined by comparing the error amplifier output to the voltage ramp at the non-inverting input of the PWM comparator. Note that this voltage ramp is the sum of the signals generated by the inductor current sense circuitry and the slope compensation circuitry. Slope compensation is added to prevent sub-harmonic oscillations for duty cycles above 50%. During each rising edge of the internal clock pulse, the power switch is turned on. The switch is turned off when the voltage ramp generated at the non-inverting input of the PWM comparator exceeds the output voltage of the error amplifier or the voltage at the inverting input of the PWM comparator.

Figure 1. AAT1267B Boost Regulator Functional Block Diagram

### Boost Soft Start (t<sub>SS</sub>)

The AAT1267B ramps up the boost regulator's current limit to achieve soft start. Soft start is either performed internally or externally. When the capacitance at the SS is lower than 200pF, soft start is performed internally by stepping up the current limit in 128 steps within 16ms. When the capacitance at SS is larger than 200pF, soft start time is controlled via an external capacitor ( $C_S$ ) connected from the SS to ground. When V<sub>1</sub> is above the UVLO threshold and the EN input is above the enable threshold, an internal 5µA current

Page 14 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

source ( $I_{SS}$ ) will begin to charge the capacitor from 0V to a nominal 1.25V ( $V_{REF}$ ). The formula is given by

$$C_{S} = t_{SS} \times \frac{I_{SS}}{V_{REF}}$$

Where  $I_{SS} = 5\mu A$ ,  $V_{REF} = 1.250V$ .

### Boost Current Limit (I<sub>CLIM</sub>)

The boost regulator current limit can be externally adjusted using the CLIM. When CLIM is left floating or R<sub>CLIM</sub> is larger than 50k $\Omega$ , the de fault current limit is 3.6A. A resistor (R<sub>CLIM</sub>) can also be connected from CLIM to ground to externally set the current limit. Use the following equation to calculate the required current limit.

$$R_{CLIM} = 1,000 \times (\frac{I_{CLIM}}{0.085} - 1)$$

### **GD** Function

Power up sequencing and true shutdown is provided for the boost regulator. The GD output drives an external PMOS that is usually placed in the path between the boost Schottky diode and the output filter capacitors. When the enable pin EN is logic low, the GD and GDI are internally connected via a low impedance path, turning off the external PMOS. Note that GDI is connected to the source of the external PMOS. When the EN pin is logic high and the negative charge pump regulator is regulating, the GD output will pull low, turning on the PMOS. Once the GD output toggles low, the boost regulator will be activated and the boost soft start will begin. When the GD function is not used, leave the GD floating and connect the GDI to the boost regulator's output.

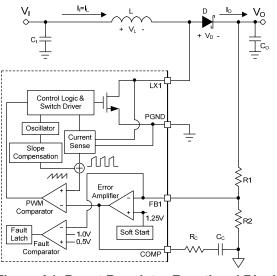

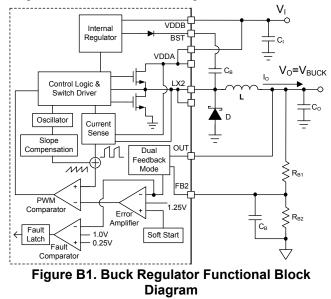

### **Buck Regulator**

This device integrates a buck regulator that includes a high side low  $R_{DSON}$  (typical 0.1 $\Omega$ ) NMOS switch, pulse width modulation (PWM) controller, built-in soft start, and internal loop compensation. An external bootstrap capacitor of 0.1 $\mu$ F connected from the switch node (LX2) to BST is used to provide the high side gate driver supply. Note that an external Schottky diode

rectifier is always required as the internal low side NMOS switch is used for charging the  $0.1\mu$ F bootstrap capacitor during startup and maintains fixed frequency operation at light load.

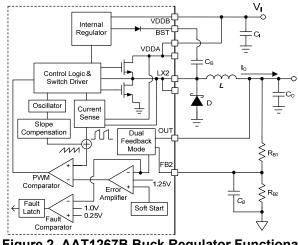

#### Figure 2. AAT1267B Buck Regulator Functional Block Diagram

The buck regulator uses the peak current mode PWM control scheme for fast transient response and cycle-by-cycle current limiting. The PWM maintains a constant frequency and varies the duty ratio according to the output voltage and load current. This modulation scheme provides high efficiency at medium to heavy load conditions, and reduces the output ripple at light load conditions. It regulates output voltage from V<sub>I</sub> down to an output voltage as low as 1.5V. The duty cycle D is calculated by

$$D = \frac{V_O}{V_I} \quad (V_O = V_{BUCK})$$

Where  $V_O$  ( $V_{BUCK}$ ) is the output voltage of the buck regulator. Typical maximum duty cycle is approximately 80%.

In this operating mode, the high side NMOS turns on each cycle for a minimum on-time, and turns off when an internal sawtooth signal exceeds the error amplifier output which monitors the buck output via a voltage resistive divider to the FB2 and compares the FB2 voltage to an internal reference of 1.25V. The sawtooth signal is composed of the sensed inductor current and

Advanced Analog Technology, Inc. –

Version 1.01

Page 15 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

an artificial slope compensation ramp to prevent oscillation at duty ratios higher than 50%. After the high side NMOS is turned off, the low-side NMOS is turned on until the next cycle begins.

### **Buck Soft Start**

In order to limit the inrush current during startup, the buck regulator has build in soft start. The soft start period is 3ms and performed internally by stepping up the current limit in 128 steps.

#### **Buck Current Limit**

The buck regulator includes cycle by cycle current limiting, with a threshold of typically 3.2A. When the current limit threshold is reached, the high side NMOS switch is turned off, releasing the inductive energy.

### **Buck Dual Mode Feedback**

This buck regulator can be configured for fixed output of 3.3V or adjustable output. For a fixed output of 3.3V, connect the FB2 directly to ground. To set the adjustable output voltage, connect a resistive network from the output (V<sub>o</sub>) to ground with the center tap to FB2, as shown in Figure 2. Use the following equation to calculate the required output voltage.

$$R_{B1} = R_{B2} \times (\frac{V_0}{V_{FB2}} - 1)$$

Where  $V_{FB2}\, is\,$  1.250V and choose  $R_{B2}$  to be between  $1k\Omega$  and  $50k\Omega.$

#### **Positive Charge Pump Regulator**

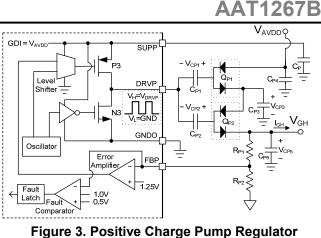

The positive regulated charge pump provides a step-up supply for the TFT LCD panel gate-on driver. The achievable output voltage is determined by the number of charge pump stages. For example, for achieving a maximum capable of approximately 3x the input voltage will require a two stage charge pump as shown in Figure 3. However, the actual regulated voltage is set by an external resistive divider from V<sub>GH</sub> to GND with center tap connected to FBP.

Functional Block Diagram

The positive charge pump consists of a high side PMOS (P3) and low side NMOS (N3) both controlled by an internal oscillator switching at 500kHz (or 750kHz). Initially, when the oscillator output is logic Low, P3 is turned off while N3 is turned on, pulling the charge pump drive output low ( $V_{DRVP}$  = GND), recharging the flying capacitors  $C_{P1}$  and  $C_{P2}$  by the input supply  $V_{AVDD}$  and  $V_{CP3}$ . Thus,

$V_{CP1} = V_{AVDD} - V_D$   $V_{CP2} = V_{CP3} - V_D$  where  $V_{CP3} = V_{AVDD} - 2V_D + V_{DRVP}$  $V_D$  = the voltage drop across the diode

When the oscillator output is logic High, P3 is turned on while N3 is turned off, pulling the charge pump drive output to a high potential  $V_{DRVP}$ , and level shifting the flying capacitors. If the output capacitors are at a lower potential, by more than a diode drop than the level shifted flying capacitors, charge will flow from the flying capacitors to the output capacitors to replenish the output charge. Thus,

$V_{CP3} = V_{AVDD} - 2V_D + V_{DRVP}$  $V_{CP5} = V_{GH} = V_{CP2} - V_D + V_{DRVP}$  $V_{GH} = V_{AVDD} - 4V_D + 2V_{DRVP}$

When  $V_{DRVP}$  is approximately equal to  $V_{AVDD}$ , the voltage at  $V_{GH}$  is approximately 3x the input voltage  $V_{AVDD}$ . This is the maximum achievable output voltage for the two stage charge pump.

When the high side PMOS is on while the low side

Advanced Analog Technology, Inc. –

Version 1.01

Page 16 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

NMOS is off, the charge pump drive output  $V_{DRVP}$  will be pulled high to a voltage magnitude that is dependent on the output power requirement. For example, as the output load increases, the feedback voltage at FBP will initially fall, increasing the error amplifier output drive strength and also the charge pump drive output voltage to a higher level. This increase in voltage of the charge pump drive output high level provides more charge to the flying capacitors and to the output for regulation. Likewise, when the output voltage during the high level will decrease.

#### **Charge Pump Flying Capacitors**

Use a  $0.1\mu$ F ~  $0.47\mu$ F for the flying capacitors (C<sub>P1</sub>, C<sub>P2</sub>) and make sure that the voltage rating (V<sub>CP</sub>) of these capacitors is adequate per the number of stages. The voltage rating of the capacitor must satisfy

$V_{CP} > n \times V_{AVDD}$

where  $V_{AVDD}$  is the input supply to the charge pumps, and n is the number of stages per charge pump. Note that the positive charge pump uses 2 stages, i.e. n = 2.

### **Charge Pump Output Capacitors**

The output capacitor  $(C_{PO})$  for the charge pump is selected to satisfy the output ripple requirement. Use ceramics for low ESR to minimize the ripple. The capacitance value can be found by

$$C_{PO} > \frac{I_{GH}}{2 \times f_{OSC} \times \Delta V_{RIPPLE}}$$

where  $\Delta V_{\text{RIPPLE}}$  is the output ripple specification,  $f_{\text{OSC}}$  is 0.5 x boost operating frequency.

### Positive Charge Pump Output Setting

The positive charge pump output voltage ( $V_{GH}$ ) is set with external resistor ladder from its output to ground with the center tap connected to FBP pin, as shown in Figure 3, Use the following equation,

$$\begin{split} R_{P1} = R_{P2} \times (\frac{V_{GH}}{V_{FBP}} - 1) \\ \text{Where } V_{FBP} \text{ is } 1.250 \text{V}, \ R_{P2} = 10 \text{k}\Omega. \end{split}$$

## AAT1267B

#### **Negative Charge Pump Regulator**

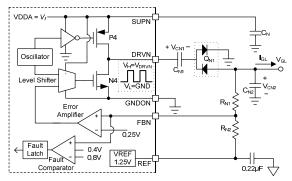

The negative regulated charge pump generates a negative supply for the TFT LCD panel gate-off driver. The maximum output voltage capability is determined by the number of charge pump stage, but the actual regulated output voltage is set via a resistive divider to REF, with the center tap connected to FBN. Typical application uses a single stage, as shown in Figure 4. The regulation scheme of the negative charge pump also consist of a high side and low side switch for charging, level shifting the flying capacitor, and drawing charge from the output.

Figure 4. Negative Charge Pump Regulator Functional Block Diagram

When the high side PMOS (P4) is turned on and the low side NMOS (N4) is off, the flying capacitor  $C_{N1}$  will charge as the upper diode will turn on and create a path to ground, and  $V_{CN1} + V_D = V_{DRVN}$ . When the drive output DRVN pulls low to near ground, the flying capacitor  $C_{N1}$  is level shifted in the negative direction, and the node connecting between  $C_{N1}$  and  $Q_{N1}$  becomes  $(-V_{CN1})$ . Thus, charge will flow from the output  $C_{N2}$  to  $C_{N1}$ , and the output can be expressed as

$$(-V_{CN1})=V_{CN2}-V_{D}\rightarrow V_{CN2}=(-V_{CN1})+V_{D}$$

$V_{CN2}=(-V_{DRVN})+2V_{D}$  where  $(V_{CN1}=V_{DRVN}-V_{D})$

The voltage magnitude of  $V_{DRVN}$  when pulled high will vary, as this voltage is dependent on the output power requirement. The maximum capable output voltage at  $V_{DRVN}$  when the P4 is fully turned ON is V<sub>I</sub>. Thus, the maximum capable output of this single stage charge pump is

$V_{GL}=V_{CN2}=(-V_I)+2V_D$

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 17 of 30

### **Charge Pump Flying Capacitors**

Use a  $0.1\mu$ F ~  $0.47\mu$ F for the flying capacitor (C<sub>N1</sub>) and make sure that the voltage rating (V<sub>CN</sub>) of these capacitors is adequate per the number of stages. The voltage rating of the capacitor must satisfy

#### $V_{CN} > n \times V_{AVDD}$

where  $V_{AVDD}$  is the input supply to the charge pumps, and n is the number of stages per charge pump. Note that the negative charge pump uses 1 stage, i.e. n = 1.

### **Charge Pump Output Capacitors**

The output capacitor  $(V_{PO})$  for the charge pump is selected to satisfy the output ripple requirement. Use ceramics for low ESR to minimize the ripple. The capacitance value can be found by

$$C_{PO} > \frac{I_{GL}}{2 \times f_{OSC} \times \Delta V_{RIPPLE}}$$

where  $\Delta V_{\text{RIPPLE}}$  is the output ripple specification,  $f_{\text{OSC}}$  is 0.5 x boost operating frequency.

### **Negative Charge Pump Output Setting**

The output voltage ( $V_{GL}$ ) of the negative charge pump is set with an external resistor ladder from its output to REF pin, with the center tap connected to FBN pin, as shown in Figure 4. Use the following equation to calculate the required output voltage

$$R_{N1} = R_{N2} \times \frac{\left(V_{GL} - V_{FBN}\right)}{\left(V_{FBN} - V_{REF}\right)}$$

where  $V_{FBN}$  is 0.250V,  $V_{REF}$  is 1.250V, and choose  $R_{N2}$  to be between  $10k\Omega$  and  $50k\Omega.$

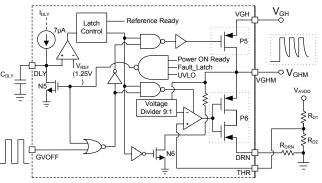

# High Voltage Switch for Gate Pulse Modulation (GPM)

An internal high voltage switch controller is included for gate pulse modulation which provides gate shaping to improve image quality in TFT LCD applications. The circuitry consist of two high voltage PMOS, one between VGH and VGHM, and another between VGHM and DRN. See Figure 5 for the Gate Pulse Modulation Functional Block Diagram. When the switch controller is enabled, logic level on the GVOFF AAT1267B

input will determine which PMOS switch is ON or OFF. If GVOFF is logic High, P5 turns on and P6 turns off, VGHM connects to VGH. If GVOFF is logic Low, P5 turns off and P6 turns on, VGHM connects to DRN, and the V<sub>GHM</sub> output is discharged via the resistor connected at DRN to ground. V<sub>GHM</sub> will discharge to 10x the voltage set at THR. Once the V<sub>GHM</sub> reaches 10 x V<sub>THR</sub>, P6 will be turned off. Note that the resistor (R<sub>DRN</sub>) value can be adjusted to different discharge time or high to low transient slope rate.

#### Figure 5. Gate Pulse Modulation Functional Block Diagram

The GPM must be enabled for the GVOFF input to control the PMOS switches. When the device supply voltage has exceeded the UVLO threshold, soft start has completed for  $V_{BUCK}$ ,  $V_{GL}$ ,  $V_{AVDD}$ ,  $V_{GH}$  or device is power on ready, and no fault condition is present, an internal 7µA current source will begin to charge the external capacitor connected to the DLY. While this capacitor is charging, the VGHM will be pulled to ground via an internal resistor and NMOS (N6). When the voltage at DLY exceeds  $V_{REF}$  (1.25V), the NMOS switch (N6) will be turned off, the GPM will be enabled, and GVOFF will control the PMOS switches as described above.

During operation, if the input supply falls below the UVLO threshold, the GPM will be immediately disabled. Instantly, the high side PMOS P5 will turn on, the low side PMOS P6 will turn off simultaneously, and GVOFF input will have no control over the PMOS switches.

Advanced Analog Technology, Inc. –

Version 1.01

Page 18 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

### **C**<sub>DLY</sub> Time Delay Setting

After device power up and soft start for the four regulators have completed, a 7 $\mu$ A current source will begin charging the external capacitor (C<sub>DLY</sub>) connected at the DLY to ground. When the voltage at the DLY exceeds V<sub>REF</sub> (1.25V), the switch control block will be enabled. The capacitor (C<sub>DLY</sub>) to set the enable delay time (t<sub>D</sub>) is chosen using the following formula.

$$C_{DLY} = t_D \times \frac{I_{DLY}}{V_{REF}}$$

where  $I_{DLY} = 7\mu A$ ,  $V_{REF} = 1.250V$

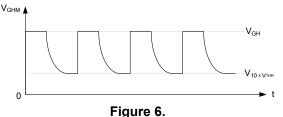

### **Discharging Stop Voltage Setting**

When the V<sub>GHM</sub> output reaches 10x the voltage set at THR, P6 will be turned off, and discharging will stop at 10 x V<sub>THR</sub>, as shown in Figure 6. The 10 x V<sub>THR</sub> voltage (V<sub>10VTHR</sub>) can be set via external resistor ladder from V<sub>AVDD</sub> to GND with the center tap connected to THR, as shown in Figure 5. Use the following equation to calculate the required setting voltage.

$$V_{THR} = V_{AVDD} \times (\frac{R_{D2}}{R_{D1} + R_{D2}}), \quad V_{10VTHR} = 10 \times V_{THR}$$

$$R_{D1} = R_{D2} \times (\frac{10 \times V_{AVDD}}{V_{10VTHR}} - 1)$$

Where  $R_{D2} = 10k\Omega$ .

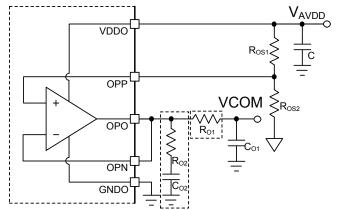

### **Operational Amplifier for VCOM Buffer**

The operational amplifier drives the LCD backplane (VCOM) or the gamma-correction divider string. The Op Amp is capable of rail-to-rail input and output,  $\pm 200$ mA output short-circuit current, and a 45V/µs slew rate. In typical application, the inverting input is shorted to the output for a voltage follower (unity gain) configuration.

In the voltage follower configuration, the capacitive load adds a pole to the loop gain that impacts the

### **AAT1267B**

stability of the system and leads to output peaking, ringing and oscillation. A higher pole frequency results in greater stability. In fact, if the pole frequency is lower than or close to the unity gain frequency, the pole can have a significant negative impact on phase and gain margins. Therefore, the stability decreases when the capacitive load increases.

One method of improving capacitive load drive is to insert a  $2\Omega$  to  $20\Omega$  resistor (R<sub>O1</sub>) in series with the output, as shown in Figure 7. This reduces ringing with large capacitive loads while maintaining DC accuracy.

Another method for improving transient response is to add a snubber circuit at the output. A snubber circuit consists of a resistor ( $R_{O2}$ ) in series with a capacitor ( $C_{O2}$ ), which improves output settling time and reduces peaking. The advantage of this topology is that it draws no DC current nor does it reduce the gain.

### Figure 7. Voltage Follower Operational Amplifier Functional Block Diagram

### VCOM Buffer Output Setting

The VCOM Buffer output voltage (VCOM) is set with external resistor ladder from its output to ground with the center tap connected to OPP pin, as shown in Figure 7, Use the following equation,

$$R_{OS1} = R_{OS2} \times (\frac{V_{AVDD}}{V_{COM}} - 1)$$

Where  $V_{AVDD}$  is the output voltage of boost regulator,  $R_{OS2}$  = 10k $\Omega$ .

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 1.01

Page 19 of 30

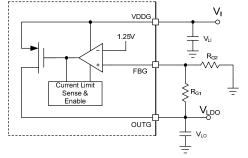

### High Accuracy LDO for Gamma Reference

Figure 8. LDO Functional Block Diagram

A high accuracy  $\pm 0.5\%$  linear regulator provides a reference to the gamma correction circuitry. This LDO rejects the ripple voltage produced by the source drivers and is capable of providing a minimum 60mA output current, see Figure 8. The output (V<sub>LDO</sub>) of the LDO is set via a resistive divider from the output to ground, with center tap connected to the FBG pin, with a feedback voltage (V<sub>FBG</sub>) of 1.250V. Set R<sub>G2</sub> between 5k $\Omega$  to 50k $\Omega$  and calculate R<sub>G1</sub> using the following equation

$R_{G1} = R_{G2} \times (\frac{V_{LDO}}{V_{FBG}} - 1) \text{ where } V_{FBG} \text{ is } 1.250 V$

### **RESET** Function (XAO)

This device has an internal reset circuit to monitor the voltage at VDET. In typical application, the input supply is monitored by connecting a resistive divider from the input (V<sub>I</sub>) to ground, with center tap connected to VDET. When the VDET voltage is lower than the threshold voltage of V<sub>VDET</sub> (1.25V), XAO output will be pulled low. XAO is an open-drain output that needs a pull-up resistor (R<sub>X</sub>=10k $\Omega$ ) to a system supply. The reset circuit is active when the device's internal regulator and reference has exceeded the UVLO threshold.

Figure 9. RESET Functional Block Diagram

As shown in Figure 9, use the following equation to calculate the required resisters of  $R_{X1}$  and  $R_{X2}$ .

$$R_{X1} = R_{X2} \times (\frac{V_l}{V_{VDET}} - 1)$$

where  $V_{VDET}$  is 1.250V and  $R_{X2}$ =10k $\Omega$ .

### Reference Voltage (VREF)

The reference output voltage is 1.250V. The reference voltage can be used to regulate the negative charge pump and source at least  $50\mu$ A. In order to have a stable reference voltage, connect a  $0.22\mu$ F ceramic bypass capacitor between REF and GND.

### **Operating Frequency Setting**

The switching frequency of the Boost and Buck regulators are controlled by the same internal oscillator, but operate  $180^{\circ}$  out of phase from each other for reducing the input RMS current. The operating frequency can be set by FSEL. If FSEL is connected to V<sub>1</sub> or is floating, the operating frequency is 750kHz. If FSEL is connected to GND, the operating frequency is 500kHz.

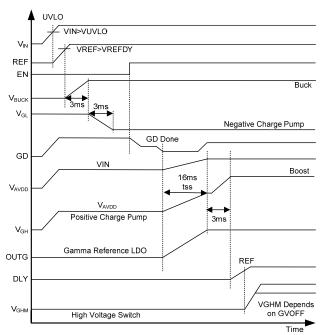

### **Power On/Off Sequence**

<sup>-</sup> 台灣類比科技股份有限公司 Advanced Analog Technology, Inc. -

Version 1.01

Page 20 of 30

The AAT1267B Power up Sequence is as shown in Figure 10. When V<sub>IN</sub> exceeds the UVLO threshold, and the internal reference (V<sub>REF</sub>) is ready, the buck regulator (V<sub>BUCK</sub>) first powers up. Once the buck regulator has completed its soft start and is in regulation, the negative charge pump (V<sub>GL</sub>) begins to power up. When the EN input is logic high, the GD output starts to turn on the external PMOS. Once GD has completely turned on the external PMOS, the boost regulator (V<sub>AVDD</sub>) and the gamma reference LDO (OUTG) will be simultaneously activated. The positive charge pump ( $V_{GH}$ ) will only begin to turn on when the boost has completed its soft start. Also note that the high voltage switch (V<sub>GHM</sub>) controller's enable delay time is dictated by the DLY capacitor charging up after the positive charge pump has completed.

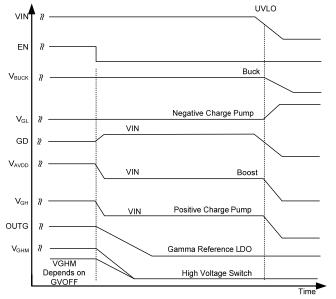

Figure 11. AAT1267B Power off Sequence

When the EN input is logic Low, the GD output will turn off the external PMOS, the boost regulator, positive charge pump, gamma reference LDO and the high voltage switch controller will be shutdown. Once  $V_{IN}$  drops below the UVLO threshold, the buck regulator and the negative charge pump will be inactivated simultaneously, see the Figure 11 for AAT1267B power off Sequence.

### AAT1267B

### **Fault Protection**

The device fault protection feature is described in Table 1. If short circuit protection (SCP) is triggered by any of the four regulators (boost, buck,  $V_{GH}$ ,  $V_{GL}$ ), no fault timer is applied, the part latches off immediately. If any one of the four regulators' feedback voltage is lower than its Fault Protection Voltage threshold (UVP), an internal fault timer of 50ms is activated. Once activated, if the fault condition surpasses the 50ms, the device will shutdown all regulators but will keep the internal reference at 1.25V. Note that fault protection is only active after all soft start events have completed. When the device is shutdown due to a fault condition, the power supply to the device must be recycled in order to restart the device.

### Thermal Shutdown

The AAT1267B device enters into fault protection shutdown when the junction temperature reaches approximately 160°C. To restart the device when the junction temperature has fallen below the thermal shutdown threshold, recycle the device supply power below the UVLO falling threshold.

- 台灣類比科技股份有限公司 -Advanced Analog Technology, Inc. -Version 1.01 Page 21 of 30

### AAT1267B

| Channel                       | Fault Condition Type                                        | Description of Fault Condition                        | Channels Disabled<br>Due to Fault                       |  |

|-------------------------------|-------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|--|

| Boost<br>(V <sub>AVDD</sub> ) | OCP                                                         | LX1 stop switching until current lower than OCP level |                                                         |  |

|                               | OVP                                                         | LX1 stop switching until voltage lower than OVP level |                                                         |  |

|                               | SCP FB1 falls below 0.5V, channel shuts down immediately    |                                                       | Vavdd, Vgh, Vgi                                         |  |

|                               | UVP                                                         | FB1 falls below 1V for more than 50ms                 | ♥AVDD, ♥GH, ♥GL                                         |  |

| Buck<br>(V <sub>виск</sub> )  | OCP                                                         | LX2 stop switching until current lower than OCP level |                                                         |  |

|                               | SCP FB2 falls below 0.25V, channel shuts dow<br>immediately |                                                       | VBUCK, VAVDD, VGH, VG                                   |  |

|                               | UVP                                                         | FB2 falls below 1V for more than 50ms                 | • BUCK, • AVDD, • GH, • GL                              |  |

| V <sub>GH</sub>               | SCP                                                         | FBP lower than 0.5V, channel shuts down immediately   | - V <sub>avdd</sub> , V <sub>gh</sub> , V <sub>gl</sub> |  |

|                               | UVP                                                         | FBP falls below 1V for more than 50ms                 |                                                         |  |

| V <sub>GL</sub>               | SCP                                                         | FBN rises above 0.8V, channel shuts down immediately  | - V <sub>AVDD</sub> , V <sub>GH</sub> , V <sub>GL</sub> |  |

|                               | UVP                                                         | FBN rises above 0.4V for more than 50ms               |                                                         |  |

# **APPLICATION NOTE**

### **Boost Regulator**

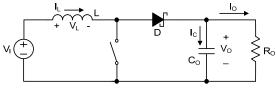

The AAT1267B integrates a current-mode, PWM Boost and NMOS switch. Figure A1 shows the AAT1267B Boost Regulator Functional Block Diagram.

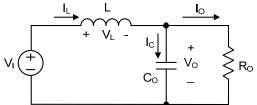

The boost regulator steps the input voltage up to higher output voltage. The basic configuration of a boost regulator can be seen in Figure A2.

Figure A2. Basic Boost Regulator Topology

The basic boost regulator operates in two time periods. The first time duration (DT<sub>S</sub>) occurs when the switch is on, and the diode is reversed biased. This results in a positive voltage  $V_L=V_I$  across the inductor. This voltage causes a linear increase in the inductor current  $I_L$ . During this "ON" period, energy is stored in the inductor and the load current is supplied by  $C_O$ .

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 22 of 30

AAT1267B

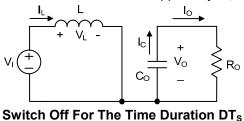

Figure A3. Switch Off For The Time Duration (1-D)T<sub>s</sub>

The next time duration is the "OFF" period of the power switch. When the switch is turned off, the diode is forward biased, and the energy stored in the inductor is transferred to the load and output capacitor. The voltage across the inductor reverses its polarity and is clamped by the diode, because of the inductive energy storage,  $I_L$  continues to flow. The current now flows through the diode, and  $V_L$ = –( $V_O$ – $V_I$ ) for a time duration (1-D)T<sub>S</sub> until the switch is turned on again.

Equating the integral of the inductor voltage over one time period to zero yields

$\int_{0}^{T_{S}} V_{L}(t) dt = \int_{0}^{DT_{S}} V_{L}(t) dt + \int_{DT_{S}}^{T_{S}} V_{L}(t) dt,$

$$(D = \frac{t_{ON}}{T_S} \text{ where } T_S \text{ is the period of switching})$$

$$V_I \times DT_S - (V_O - V_I) \times (1 - D)T_S = 0$$

$V_{I} = (1-D)V_{O, I} \frac{V_{O}}{V_{I}} = \frac{1}{1-D}$

### Component Selection for Boost Regulator Inductor Selection (L)

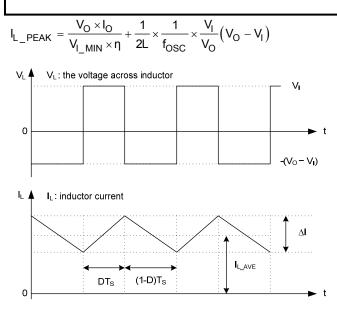

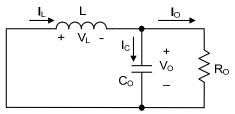

The value of the inductor is calculated based on the input V<sub>1</sub> and output voltage V<sub>0</sub>, switching frequency  $f_{OSC}$ , and the nominal output load current I<sub>0</sub>. However, when selecting the optimal inductance, both the regulator's performance and the inductor size or cost must be considered. According to the operating relationship between inductor voltage and inductor current shown in Figure A4, the Inductor ripple current ( $\Delta$ I) can be calculated by the following equation.

$$iL(t) = iL(0) + \frac{1}{L} \int V_{L}(t)dt, \ \left(T_{S} = \frac{1}{f_{OSC}}, \ \frac{V_{O}}{V_{I}} = \frac{1}{1-D}\right)$$

$$\Delta I = \frac{1}{L} V_{I} \times DT_{S} = -\frac{1}{L} (V_{O} - V_{I}) \times (1 - D)T_{S}$$

$$\Delta I = \frac{1}{L} \times \frac{1}{f_{OSC}} \times \frac{V_{I}}{V_{O}} (V_{O} - V_{I})$$

And obtain Inductance L

$$L = \frac{1}{\Delta I} \times \frac{1}{f_{OSC}} \times \frac{V_I}{V_O} (V_O - V_I),$$

$$\left(\eta = \frac{V_{O} \times I_{O}}{V_{I} \times I_{I}}, \quad L_{IR} = \frac{\Delta I}{I_{I}} = \frac{\eta \times V_{I}}{V_{O} \times I_{O}} \times \Delta I\right)$$

$$L = \frac{\eta}{L_{IR}} \times \frac{1}{f_{OSC}} \times (\frac{V_{I}^{2} \times (V_{O} - V_{I})}{V_{O}^{2} \times I_{O}})$$

Where  $L_{IR}$  is the ratio of the ripple current ( $\Delta I$ ) to input current ( $I_I$ ) at the full load current, and  $\eta$  is efficiency.

Although using a small inductance can decrease component size or cost and increase the regulator's response time, inductor ripple current increases which results in high output ripple and in lower efficiency due to increase conduction losses. Using a large inductance can lower ripple current to mitigate conduction losses and minimize output ripple, but too large of an inductance leads to slow response time and lower efficiency if the losses from the higher DCR outweigh the losses eliminated from lower ripple current. The inductor ripple current is usually adjusted by the system designer based on application for the desired cost and performance.

After selecting the inductance value, the inductor's saturation current rating should be chosen to exceed the inductor ripple current for the lowest input voltage  $V_{I \text{ MIN}}$  in the application.

$$I_{L\_AVE(MAX)} = \frac{V_O \times I_O}{V_{l\_MIN} \times \eta} \ \left( where \ \eta = \frac{V_O \times I_O}{V_l \times I_l} \right)$$

And Inductor peak current  $I_{L\_PEAK}$

$$I_{L}PEAK = I_{L}AVE(MAX) + \frac{1}{2}\Delta I$$

Advanced Analog Technology, Inc. –

Version 1.01

Page 23 of 30

Figure A4. Inductor Voltage vs. Inductor Current (CCM)

For boost regulator,  $L_{IR}$  is usually chosen to be 0.3 to 0.5. However, if the inductor used in the TFT LCD application has significant wire resistance, higher  $L_{IR}$  (above 0.5) can be used to lower the inductance value and therefore lower the total DCR.

#### **Output Capacitor Selection (Co)**

For switching regulators, output capacitance is chosen based on the desired output ripple and/or output voltage deviation based on a given load change.

The output voltage ripple consists of both the inductor ripple current flowing through the capacitor ESR (equivalent series resistance), and the transfer of charge to and from the output capacitor. Since in TFT LCD display applications, ceramic capacitors are used at the output, the ripple due to the IR effect can be neglected since ceramics capacitors have extremely low ESR. Thus the ripple due to the charge and discharge of the output capacitor will be dominant. Based on a desired ripple, the minimum output capacitance can be calculated by. (Please refer to the Figure A5)

where  $\Delta V_0$  is the output ripple voltage specification.

Note that ceramic capacitors are often used for their size advantage and environmentally-friendly nature. To achieve the required ripple or output capacitance value, multiple ceramic capacitors are often connected in parallel.

### Input Capacitors Selection (C<sub>I</sub>)

Input capacitors are usually a combination of bulk capacitor and high frequency ceramic. The bulk capacitor serves as the power source during the soft start process, supplies switching current, minimizes input ripple, and keeps the DC input voltage stable. The bulk capacitor is usually chosen to support the input RMS current, and can also be ceramic type. Often, extra bulk capacitance is added during bench

Advanced Analog Technology, Inc. –

Version 1.01

Page 24 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

evaluation to alleviate the parasitic inductance introduced from the power supply cable.

The high frequency ceramic capacitor filters the high frequency noise to the device. Usually, a  $0.1\mu$ F to  $1\mu$ F ceramic capacitor is used. A RC low-pass filter is often added to decrease interference from noise.

### **Diode Selection (D)**

The diode voltage rating must be greater than the output voltage  $V_O$  and the current rating must exceed the inductor peak current  $I_{L_PEAK}$ . Using a diode with low forward voltage drop and fast recovery time to minimize the conduction loss and switching loss, and then help increase efficiency, such as a Schottky rectifier is recommended.

### **Output Voltage Selection (Vo)**

The output voltage is set using a resistive voltage divider from the output to FB1, referenced to analog ground as shown in Figure A1. Use the following equation to set the boost voltage, or  $V_{O}$ ,

$$R_1 = R_2 \times (\frac{V_0}{V_{FB1}} - 1)$$

where  $V_{FB1}$  is 1.250V and  $R_2$ =10k $\Omega$ .

### **Crossover Frequency Selection**

The crossover frequency, or the regulator bandwidth, is usually selected to satisfy the output step load requirement. However, due to the inherent nature of the CCM boost, a right-half-plane-zero (RHPZ) will limit the selection of the crossover frequency ( $f_c$ ) due to its phase lag. A good design rule is to select the crossover frequency to be about 20% of the RHPZ frequency. The RHPZ frequency is given by

$$f_{RHPZ} = \frac{R_O \times (1-D)^2}{2\pi \times L} \text{ where } R_O = \frac{V_O}{I_O}$$

$f_C \text{=} 0.2 \times f_{\text{RHPZ}}$

### Compensation Selection (R<sub>c</sub> & C<sub>c</sub>)

To stabilize the boost regulator's loop, a RC series network is added from the COMP output pin to analog ground. See Figure A1.  $R_C$  is chosen to set the

amplifier gain for a targeted crossover frequency. Setting the total loop gain to unity gain at the desire crossover frequency, we can calculate  $R_c$  by approximately

$$R_{C} = 0.3 \times \frac{V_{O}}{V_{FB1}} \times \frac{V_{O}}{V_{I}} \quad \times \frac{\pi \times f_{C} \times C_{O}}{g_{m} \times g_{CS}}$$

Where  $g_m$ =105µS is the feedback error amplifier transconductance,  $g_{CS}$ =4S is the current sense transconductance, the crossover frequency of the regulator  $f_C$ =20%× $f_{RHPZ}$ , and  $V_{FB1}$  is the feedback reference voltage of 1.24V. In typical application, RC value ranges from 10k $\Omega$  to 100k $\Omega$ .

Once  $R_c$  is selected,  $C_c$  is adjusted to place a zero for neutralizing the output pole caused by the output capacitance  $C_o$  and load  $R_o$ . Use the following equation to calculate  $C_c$ ,

$$C_{C} = \frac{C_{O} \times R_{O}}{50 \times R_{C}}$$

In typical application,  $C_{\text{C}}$  value ranges from 680pF to 2.2nF.

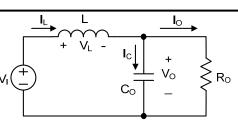

#### **Buck Regulator**

The AAT1267B integrated a current-mode, PWM Buck Regulator. Figure B1 shows the AAT1267B Buck Regulator Functional Block Diagram.

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 1.01

Page 25 of 30

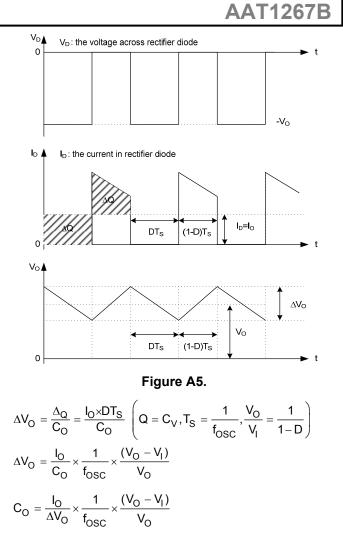

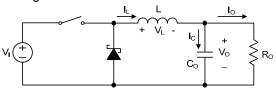

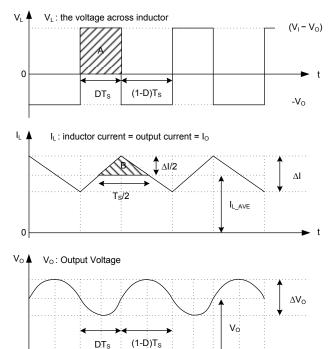

The Buck Regulator is the most elementary forward–mode regulator. Its basic schematic can be seen in Figure B2.

Figure B2. Basic Buck Regulator Topology

The operation of this regulator topology has two distinct time periods. The first one occurs when the switch is on for the time duration  $DT_s$ , the switch conducts the inductor current and the diode becomes reverse biased. This results in a positive voltage  $V_L = V_I - V_O$  across the inductor. This voltage causes a linear increase in the inductor current  $I_L$ . During this "ON" period, energy is stored within the core material in the form of magnetic flux. If the inductor is properly designed, there is sufficient energy stored to supply the requirements of the load during the "OFF" period.

Switch On for the Time Duration DTs

Figure B3. Switch Off For the Time Duration (1-D)  $T_S$

The next period is the "OFF" period of the power switch. When the switch is turned off, the voltage across the inductor reverses its polarity and is clamped by the diode, because of the inductive energy storage,  $I_L$  continues to flow. The current now flows through the diode, and  $V_L = -V_O$  for a time duration  $(1-D)T_S$  until the switch is turned on again. Equating the integral of

the inductor voltage over one time period to zero yields

$$\begin{array}{l} T_{S} \\ \stackrel{}{_{O}} V_{L}(t) dt = \int \limits_{0}^{DT_{S}} V_{L}(t) dt + \int \limits_{DT_{S}}^{T_{S}} V_{L}(t) dt, \\ (D = \frac{t_{ON}}{T_{S}} \quad \mbox{where } T_{S} \mbox{ is the period of switching}) \\ (V_{I} - V_{O}) \times DT_{S} + (-V_{O}) \times (1 - D)T_{S} = 0 \\ V_{O} = DV_{I}, \quad \frac{V_{O}}{V_{I}} = D \end{array}$$

Assuming a lossless circuit  $P_I = P_{O_i}$  Therefore  $P = V_I \times I_I = V_O \times I_O$ , and  $\frac{I_O}{I_I} = \frac{V}{V_O} = \frac{1}{D}$

For a buck regulator, it is obvious that

According to the buck operating relationship between inductor and output capacitor, shown in Figure B4, The peak-to-peak inductor current ripple  $\Delta I_L$  can be calculated by following equation.

$$i_{L}(t) = i_{L}(0) + \frac{1}{L} \int V_{L}(t) dt,$$

$(T_{S} = \frac{1}{f_{OSC}}, \frac{V_{O}}{V_{I}} = D)$

$\Delta I_L = \frac{1}{L} [Shaded area under waveform V_L (Area A)]$

$$\Delta I_{L} = \frac{1}{L} (V_{I} - V_{O}) \times DT_{S} = \frac{1}{L} (-V_{O}) \times (1 - D)T_{S}$$

$$\Delta I_{L} = \frac{1}{L} \times \frac{1}{f_{OSC}} \times \frac{V_{O}}{V_{I}} (V_{I} - V_{O})$$

From  $\Delta I_L,$  we can obtain  $I_{L\_MIN}$  and  $I_{L\_MAX}$

$$I_{L_MIN} = I_L - \frac{\Delta I_L}{2}$$

$$I_{L_MAX} = I_L + \frac{\Delta I_L}{2}$$

The peak-to-peak output voltage ripple,  $\Delta V_O$

$$\Delta V_{O} = \Delta V_{C} = \frac{1}{C} \int IC(t)dt, \qquad (Q = C \times V)$$

$$\Delta V_{O} = \frac{1}{L} \left[ \text{Shaded area under waveform } I_{L} \text{ (Area B)} \right]$$

$$\Delta V_{O} = \frac{1}{C} \times \frac{1}{2} \times \frac{T_{S}}{2} \times \frac{\Delta I_{L}}{2}$$

$$\Delta V_{\rm O} = \frac{1}{8} \times \frac{1}{f_{\rm OSC}} \times \frac{\Delta I_{\rm L}}{C}$$

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. – Version 1.01

Page 26 of 30

### Component Selection for Buck Regulator Inductor Selection (L)

The inductance (L), saturation current rating and DC resistance (DCR) of the inductor are important parameters to consider when selecting the inductor, since these parameters affect the regulator's performance and efficiency. Base on the input V<sub>1</sub> and output voltage V<sub>o</sub>, switching frequency  $f_{OSC}$ , and the output load current I<sub>o</sub>, the inductance (L) can be calculated by the following equation.

### Figure B4. The operating waveform of a Buck Regulator

$$\begin{split} \Delta I_L &= \frac{1}{L} \times \frac{1}{f_{OSC}} \times \frac{V_O}{V_I} (V_I - V_O) \\ L &= \frac{1}{L_{IR} \times I_O} \times \frac{1}{f_{OSC}} \times \frac{V_O}{V_I} (V_I - V_O), \ \left( L_{IR} = \frac{\Delta I}{I_O} \right) \end{split}$$

Where  $L_{IR}$  is the ratio of peak to peak inductor current ripple ( $\Delta I$ ) to the load current  $I_O$ , and is usually set at 20%~40% of  $I_O$ . Although using a lower inductance minimizes physical size and cost, a lower inductance increases inductor current ripple and reduces the efficiency due to higher peak currents. On the other

### AAT1267B

hand, a higher inductance reduces the ripple current to mitigate conduction losses and minimize output voltage ripple, but too large of an inductance leads to slow response time and lower efficiency if the losses from the higher DCR outweigh the losses eliminated from a lower ripple current.

Peak current through the inductor determines the inductor's required saturation current rating, the maximum inductor current  $I_{LMAX}$  as shown below.

$$I_{LMAX} = I_O + \frac{\Delta I_L}{2}$$

During power up, faults or transient load conditions, the inductor current can increase above the calculated peak inductor current level. In transient conditions, the inductor current can increase up to the switch current limit of the device. For these reasons, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

The DC resistance is the wire resistance of an inductor, and will result in power dissipation due to the current flowing through the inductor. Hence, the inductor DCR should be kept low for good efficiency.

### Input Capacitor Selection (C<sub>I</sub>)

The input current of the buck regulator is discontinuous, and depending on the load input peak currents can be large, causing large input voltage ripple and noise. Hence the input capacitor must be able to support the maximum input operatin voltage and the maximum RMS input current. Since the input capacitor has to absorb switching current, it requires an adequate ripple current rating. The RMS input current ( $I_{I_RMS}$ ) can be calculated as follows.

$$I_{I\_RMS} = \frac{I_{O}}{V_{I}} \times \sqrt{V_{O}(V_{I} - V_{O})}$$

In the worst case, with a duty cycle of 50%,

$$D = \frac{1}{2} = \frac{V_O}{V_I}, \ I_{I\_RMS} = \frac{I_O}{V_I} \times V_O = \frac{I_O}{2}$$

Advanced Analog Technology, Inc. – Version 1.01 Page 27 of 30

<sup>-</sup> 台灣類比科技股份有限公司 -

For best performance, use a low ESR input capacitor to prevent large voltage transients from appearing at the input, and to minimize power dissipation. A ceramic type capacitor is recommended because of their high RMS current rating and low ESR for a given physical dimension.

### **Output Capacitor Selection (Co)**

The output capacitor ( $C_O$ ) functions to store energy, to maintain the output voltage, and to stabilize the regulation control system. The output capacitor is chosen to meet the output ripple specification and to provide storage for load transients. The ESR of the output capacitor and the peak–to–peak value of the inductor ripple current are the main factors contributing to the output ripple voltage value ( $\Delta V_O$ ). The output ripple voltage is approximated by

$$\Delta V_{O} = \Delta I_{L} \times \left( \mathsf{ESR} + \frac{1}{8 \times f_{OSC} \times C_{O}} \right)$$

For low output ripple voltage, low ESR output capacitors are recommended. When a low ESR ceramic capacitor is used, the output voltage ripple due to the ESR is small and can be ignored. In this case the output ripple is mainly attributed to the capacitor charging and discharging. Note that choosing a capacitor with very low ESR may cause the regulator system to be unstable.

The desired output voltage change during a load transient also determines the output capacitance requirement. For a given voltage change  $\Delta V_0$ , and a given load change  $\Delta I_0$ , the output capacitance (C<sub>0</sub>) can be calculated by

$$C_{O} = \frac{L \times \left(I_{O} + \frac{1}{2} \Delta I_{O}\right)^{2}}{\left(\Delta V_{O} + V_{O}\right)^{2} - {V_{O}}^{2}}$$

Where  $\Delta I_{O}$  is the change in output current, and  $\Delta V_{O}$  is the allowable change in the output voltage.

### Rectifier Diode Selection (D)

Since the rectifier diode is a very significant source of power loss in switching power supplies, Schottky diodes are recommended for most application because of their fast recovery time and low voltage drop. Choose a rectifier with a peak voltage greater than the maximum input voltage, and the peak current rating should exceed the maximum inductor current.

### **Bootstrap Capacitor Selection (CB)**