### Product information presented is for internal use within AAT Inc. only. Details are subject to change without notice <u>MULTI-CHANNEL POWER SUPPLY FOR TFT LCD PANELS</u> <u>FULLY I<sup>2</sup>C INTERFACE CONTROL – TWO BOOST, CHARGE PUMP, BUCK/LDO</u> <u>GPM, PVCOM, TWO OPERATIONAL AMPLIFIER, RESET</u>

# **FEATURES**

- 2.5V to 5.5V Input Supply Voltage Range

- Fully I<sup>2</sup>C Interface Control

- Current Mode Boost Regulator for V<sub>AVDD</sub>

- ◆ 3.6V to 12.7V Output Voltage Range

- Current Mode Boost Regulator for V<sub>GH</sub>

- ◆ 10V to 37V Output Voltage Range

- ◆ Temperature Compensation (T/C)

- Alternative Buck Regulator or Low Dropout Linear Regulator for V<sub>25</sub>

- ◆ 1.5V to 3.0V Output Voltage Range

- Negative Charge Pump Linear Regulator for V<sub>GL</sub>

- ◆ -4.5V to -8.0V Output Voltage Range

- Unit-Gain Buffer for V<sub>COM</sub>

- ◆ 7 Bits, 128-Step Adjustable Sink Current Output

- ◆ ±200mA Short-Circuit Current

- ♦ 12V/µs Slew Rate

- ◆ Temperature Compensation (T/C)

- Two Operational Amplifier

- ±120mA Short-Circuit Current

- ♦ 12V/µs Slew Rate

- Gate Pulse Modulation (GPM)

- RESET Output (XAO)

- Open Drain Output

- Protection

- Over Voltage Protection (OVP)

- Under Voltage Protection (UVP)

- Short Circuit Protection (SCP)

- Over Temperature Protection (OTP)

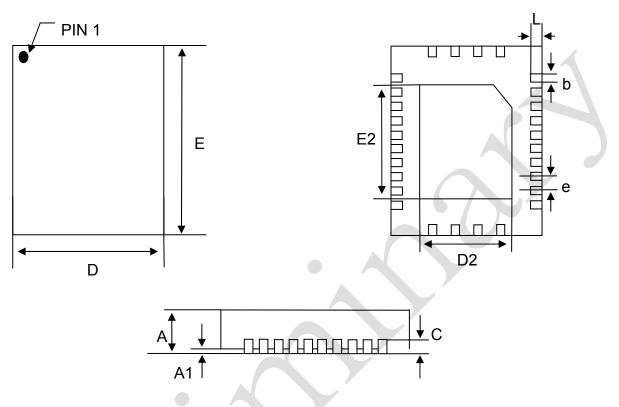

- WQFN 28-3.5mmX5.5mmX0.75mm Package

# **GENERAL DESCRIPTION**

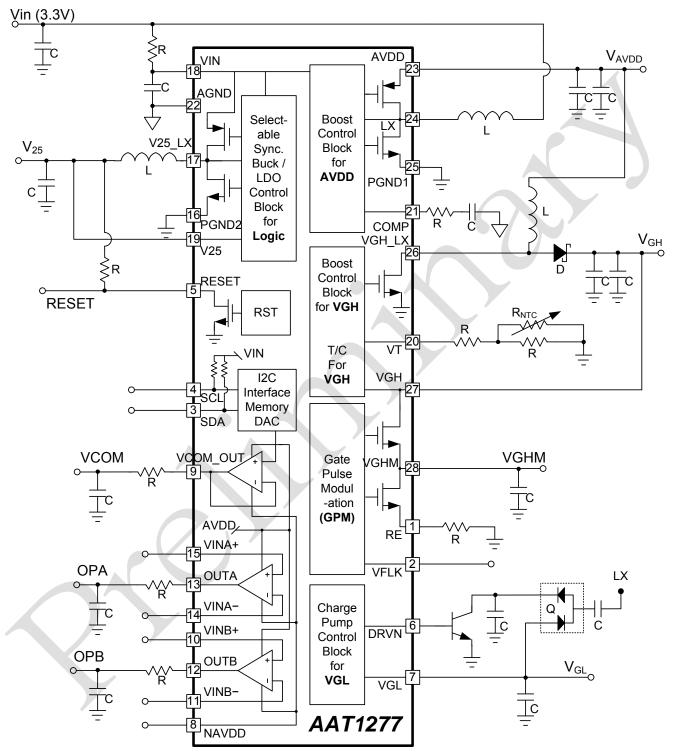

The AAT1277 is a highly integrated power management IC for TFT LCD panels. The device consists of two current mode boost regulators, a current mode buck regulator or a low dropout linear regulator alternatively, a negative charge pump linear regulator, a gate pulse modulation, a reset function, a unit-gain VCOM buffer and two operational amplifiers. The AAT1277 also includes I<sup>2</sup>C interface for setting various parameters such as each regulator's output voltage, switching frequency, soft start time, delay times, etc.

The AAT1277 includes a current mode synchronous boost regulator that provides a fast transient response supply voltage for the source driver. The source driver boost is capable of generating up to 12.7V. A second current mode non-synchronous boost supplies the gate-on voltage, and is capable of an output voltage of up to 37V. The VGH boost includes a temperature compensation function. For improving TFT LCD image quality, a gate pulse modulation (GPM) circuit shapes the gate-on signal. The slope of the gate-on voltage can be set by external resistor.

The logic power voltage (V25) could be supplied either by the buck regulator or by LDO alternatively and programmed via I<sup>2</sup>C from 1.5V to 3V. The synchronous current mode buck regulator operates at a fixed switching frequency of 1.2MHz, and provides fast load transient response to pulsed loads while producing efficiencies over 90%. The low dropout linear regulator (LDO) output voltage guarantees a minimum 350mA output current limit.

The AAT1277 negative charge pump linear regulator generates VGL supply voltage for the gate-off voltage.

The programmable operational amplifier drives the LCD backplane (VCOM). This unity-gain buffer is capable of

- 台灣類比科技股份有限公司 -

- Advanced Analog Technology, Inc. -

Version 0.03

Page 1 of 44

Advanced Analog Technology, Inc.

**AAT1277**

rail-to-rail input and output,  $\pm 200$ mA output short-circuit current, and a 12V/µs slew rate. Output voltage can be programmed by I<sup>2</sup>C interface using 7-bits or 128 steps, eliminating mechanical potentiometers to reduce labor cost.

Two operational amplifiers are included for the Panel repair-line. Those are not controlled by  $I^2C$  interface and their outputs are set using an external signal.

The reset functions (RESET) is used to monitor the V25 voltage. The reset signal is issued via an open drain NMOS when the supply is below a programmable thresholds voltage.

The AAT1277 device includes various protection features such as input under-voltage lockout (UVLO) and

over temperature shutdown (OTP). Regulator outputs include under voltage protection (UVP), overload voltage protection (OVP), and short circuit protection (SCP).

The AAT1277 is available in a small WQFN 28 pin 3.5mmX5.5mmX0.75mm with a bottom side exposed thermal pad to provide optimal heat dissipation. The device is rated to operate from -40 to +85°C temperature range.

# **APPLICATIONS**

- Tablet Panel

- Notebook Panel

# **ORDERING INFORMATION**

| DEVICE<br>TYPE | PART<br>NUMBER    | PACKAGE                    | PACKING             | TEMP. RANGE      | MARKING                | MARKING<br>DESCRIPTION                                      |

|----------------|-------------------|----------------------------|---------------------|------------------|------------------------|-------------------------------------------------------------|

| AAT1277        | AAT1277<br>-Q45-T | Q45:<br>WQFN28-<br>3.5X5.5 | T: Tape<br>and Reel | –40 °C to +85 °C | 1277<br>XXXXXX<br>XXXX | Device Type<br>Lot no. (6~9 Digits)<br>Date Code (4 Digits) |

Note: All AAT products are lead free and halogen free.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 2 of 44

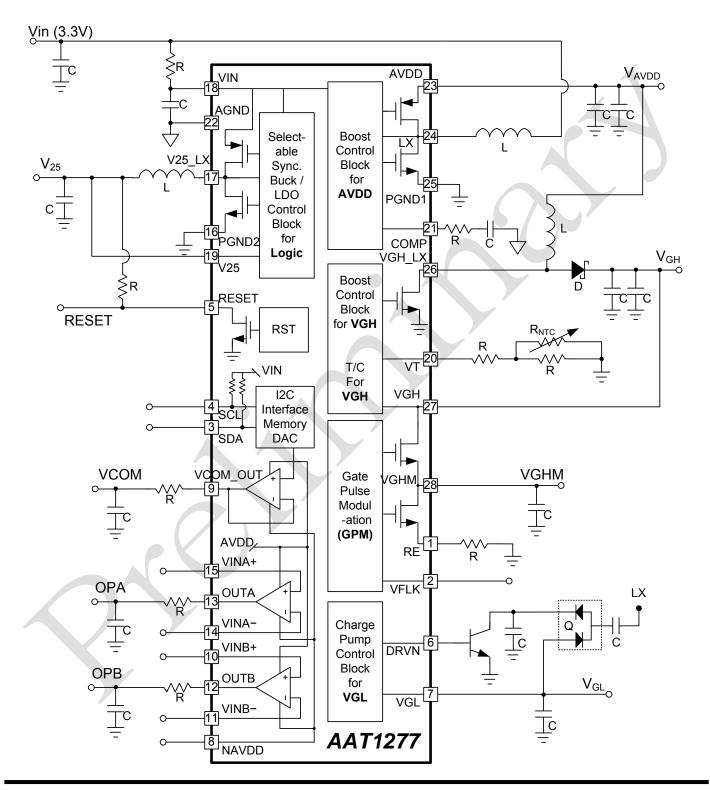

**TYPICAL APPLICATION**

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 3 of 44

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                              | SYMBOL               | VALUE                          | UNIT |

|------------------------------------------------------------------------|----------------------|--------------------------------|------|

| VIN to AGND                                                            | V <sub>IN</sub>      | -0.3 to +6.5                   | V    |

| PGND1, PGND2 to AGND                                                   | -                    | -0.3 to +0.3                   | V    |

| LX to PGND1                                                            | V <sub>H1</sub>      | -0.3 to +16.0                  | V    |

| V25_LX to PGND2                                                        | V <sub>H2</sub>      | -0.3 to +6.5                   | V    |

| VGH_LX to PGND1                                                        | V <sub>H3</sub>      | -0.3 to +45.0                  | V    |

| DRVN to PGND1                                                          | V <sub>H4</sub>      | -12.0 to +0.3                  | V    |

| Input Voltage 1 (SCL, SDA, V25, VFLK)                                  | V <sub>I1</sub>      | –0.3 to V <sub>IN</sub> +0.3   | V    |

| Input Voltage 2 (AVDD)                                                 | V <sub>I2</sub>      | –0.3 to V <sub>H1</sub> +0.3   | V    |

| Input Voltage 3 (NAVDD)                                                | V <sub>I3</sub>      | V <sub>H4</sub> –0.3 to +0.3   | V    |

| Input Voltage 3 (VGH)                                                  | V <sub>I4</sub>      | –0.3 to V <sub>H3</sub> +0.3   | V    |

| Input Voltage 4 (VGL)                                                  | V <sub>I4</sub>      | V <sub>H4</sub> -0.3 to +0.3   | V    |

| Output Voltage 1 (COMP, VT, RESETB)                                    | V <sub>01</sub>      | –0.3 to V <sub>IN</sub> +0.3   | V    |

| Output Voltage 2<br>(VCOM_OUT, OUTA, OUTB, VINA+, VINB+, VINA–, VINB–) | V <sub>O2</sub>      | $V_{H4}$ –0.3 to $V_{H1}$ +0.3 | V    |

| Output Voltage 3 (VGHM, RE)                                            | V <sub>O3</sub>      | –0.3 to $V_{H3}$ +0.3          | V    |

| Operating Ambient Temperature Range                                    | T <sub>A</sub>       | -40 to +85                     | °C   |

| Operating Junction Temperature Range                                   | TJ                   | -40 to +150                    | °C   |

| Storage Temperature Range                                              | T <sub>STORAGE</sub> | –65 to +150                    | °C   |

| Package Thermal Resistance                                             | θ <sub>JA</sub>      | 31.88                          | °C/W |

| Power Dissipation, @ $T_A$ = +25 ° C , $T_J$ = +125 ° C                | P <sub>d</sub>       | 3.137                          | W    |

| ESD Susceptibility Human Body Mode                                     | НВМ                  | 2k                             | V    |

| ESD Susceptibility Machine Mode                                        | MM                   | 200                            | V    |

Note:

1. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device.

2. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.5V \text{ to } 5.5V, T_A = -40 \degree \text{C} \text{ to } +85 \degree \text{C}$ , unless otherwise specified. Typical values are tested at +25 °C ambient temperature,  $V_{IN} = 3.3V$ ,  $V_{AVDD} = 8.5V$ ,  $V_{GH} = 23V$ ,  $V_{GL} = -6V$ ,  $V_{25} = 2.5V$ , NAVDD = GND)

#### **Operating Power**

| PARAMETER                       | SYMBOL            | TEST CONDITION    | MIN      | TYP  | МАХ  | UNIT |

|---------------------------------|-------------------|-------------------|----------|------|------|------|

| VIN Input Voltage Range         | V <sub>IN</sub>   |                   | 2.5      | -    | 5.5  | V    |

|                                 |                   | Rising            | 2.30     | 2.35 | 2.40 | V    |

| Under Voltage Lockout Threshold | V <sub>UVLO</sub> | Falling           | 2.1      | 2.2  | 2.3  | V    |

| -                               |                   | Hysteresis        | 100      | 150  | 200  | mV   |

|                                 | I <sub>IN</sub>   | Not Switching     | ( - /    |      | 2    | mA   |

| Quiescent Current               |                   | Switching         | -(       | 6    | -    | mA   |

| Thermal Shutdown                | T <sub>SH</sub>   |                   | -        | 150  | -    | °C   |

| Supply Current Into AVDD        |                   |                   | <b>_</b> | 5.0  | 8.5  | mA   |

| Supply Current Into VGH         |                   |                   | -        | 0.1  | 1.0  | mA   |

| VIN Stress                      |                   | Pulse Width 100ms | -        | -    | 12   | V    |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.5V \text{ to } 5.5V, T_A = -40 \degree \text{C} \text{ to } +85 \degree \text{C}$ , unless otherwise specified. Typical values are tested at +25 °C ambient temperature,  $V_{IN} = 3.3V$ ,  $V_{AVDD} = 8.5V$ ,  $V_{GH} = 23V$ ,  $V_{GL} = -6V$ ,  $V_{25} = 2.5V$ , NAVDD = GND)

### Synchronous Current Mode Boost Regulator (V<sub>AVDD</sub>)

| PARAMETER                      | SYMBOL                  | TEST CONDITION                                                      | MIN   | TYP                                                                                                                          | МАХ   | UNIT |

|--------------------------------|-------------------------|---------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|-------|------|

| AVDD Output Voltage Accuracy   |                         |                                                                     | -1    | -                                                                                                                            | +1    | %    |

| AVDD Output Voltage Range      | V <sub>AVDD</sub>       | 7Bits, Step = 0.1V                                                  | 3.60  | 0                                                                                                                            | 12.7  | V    |

| LX Opsillation Fragmanny       | £                       | 2 Bits, Step = 200kHz                                               | 600   | <u> </u>                                                                                                                     | 1200  | kHz  |

| LX Oscillation Frequency       | f <sub>OSC_AVDD</sub>   | Tolerance                                                           | -20   | -                                                                                                                            | +20   | %    |

| IX Current Limit               |                         | 1 Bits, Step = 1A<br>Tolerance ±20%                                 | 0.8   | 1.0                                                                                                                          | 1.2   | А    |

| LX Current Limit               | I <sub>LIM_LX</sub>     |                                                                     | 1.6   | 2.0                                                                                                                          | 2.4   | А    |

| LX NMOS ON-Resistance          | R <sub>ON1_NMOS</sub>   |                                                                     | -     | 0.2                                                                                                                          | 0.3   | Ω    |

| LX NMOS Leakage Current        | I <sub>Leak1_NMOS</sub> |                                                                     | )-    | 10                                                                                                                           | 20    | μA   |

| LX PMOS ON-Resistance          | R <sub>ON1_PMOS</sub>   |                                                                     | -     | 0.8                                                                                                                          | -     | Ω    |

| LX PMOS Leakage Current        | I <sub>Leak1_PMOS</sub> |                                                                     | -     | 1                                                                                                                            | 20    | μA   |

| LX Maximum Duty Cycle          | D <sub>MAX_LX</sub>     | $V_{IN}$ = 2.5, $V_{AVDD}$ = 11V,<br>H = 0.8, $f_{OSC_LX}$ = 1.2MHz | 79.8  | 81.8                                                                                                                         | -     | %    |

| Line Regulation                | V <sub>LINE_AVDD</sub>  | V <sub>IN</sub> = 2.5V to 5.5V,<br>I <sub>AVDD</sub> = 200mA        | -     | ±0.1                                                                                                                         | ±0.15 | %/V  |

| Load Regulation                | VLOAD_AVDD              | V <sub>IN</sub> = 3.3V,<br>I <sub>AVDD</sub> = 20 to 200mA          | -1    | -                                                                                                                            | +1    | %    |

| Coff Start Time                |                         | 2 Bits, Step = 20ms                                                 | 20    | -                                                                                                                            | 80    | Ms   |

| Soft Start Time                | t <sub>ss_avdd</sub>    | Tolerance                                                           | -10   | $0.2$ $0.3$ $10$ $20$ $0.8$ - $1$ $20$ $81.8$ - $\pm 0.1$ $\pm 0.15$ $\pm 0.1$ $\pm 0.15$ $ +10$ $ +10$ $ 1.1$ $15.0$ $15.5$ | +10   | %    |

| LX Switch ON / OFF Slew Rate   | TS <sub>LX</sub>        | 2 Bits, Step = 0.2 V/ns                                             | 0.5   | -                                                                                                                            | 1.1   | V/ns |

| Over Meltage Drotect Meltage   | N                       |                                                                     | 14.5  | 15.0                                                                                                                         | 15.5  | V    |

| Over Voltage Protect Voltage   | V <sub>OVP_AVDD</sub>   | Hysteresis                                                          | 1.129 | 1.250                                                                                                                        | 1.375 | V    |

| (Inder)/oltage Drotect)/oltage |                         |                                                                     | 75    | 80                                                                                                                           | 85    | %    |

| Under Voltage Protect Voltage  | V <sub>UVP_AVDD</sub>   | V <sub>AVDD</sub> Rising – V <sub>AVDD</sub> Falling                | 0.5   | 1.5                                                                                                                          | 2.5   | %    |

| Duration to UVP Trigger Time   | t <sub>UVP_AVDD</sub>   |                                                                     | 140   | 160                                                                                                                          | 180   | Ms   |

| Short Circuit Protect Voltage  | V <sub>SCP_AVDD</sub>   |                                                                     | 25    | 30                                                                                                                           | 35    | %    |

# **ELECTRICAL CHARACTERISTICS**

$(V_{\text{IN}} = 2.5\text{V to } 5.5\text{V}, \text{ } T_{\text{A}} = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are tested at } +25\,^{\circ}\text{C} \text{ ambient temperature, } V_{\text{IN}} = 3.3\text{V}, \text{ } V_{\text{AVDD}} = 8.5\text{V}, \text{ } V_{\text{GH}} = 23\text{V}, \text{ } V_{\text{GL}} = -6\text{V}, \text{ } V_{25} = 2.5\text{V}, \text{ } \text{NAVDD} = \text{GND})$

### Current Mode Boost Regulator (V<sub>GH</sub>)

| PARAMETER                     | SYMBOL                         | TEST CONDITION                                                         | MIN  | TYP  | MAX  | UNIT |

|-------------------------------|--------------------------------|------------------------------------------------------------------------|------|------|------|------|

| VGH Output Voltage Accuracy   | N                              |                                                                        | -1   | -    | +1   | %    |

| VGH Output Voltage Range      | V <sub>GH</sub>                | 5 Bits, Step = 1V                                                      | 10   | -    | 37   | V    |

|                               | £                              |                                                                        | 320  | 400  | 480  | kHz  |

| VGH_LX Oscillation Frequency  | f <sub>osc_vgн</sub>           | 1 Bits, Step = 400kHz                                                  | 640  | 800  | 960  | kHz  |

| VGH_LX Current Limit          | I <sub>LIM_ VGH</sub>          |                                                                        | 1.2  | 1.5  | 1.8  | А    |

| VGH_LX NMOS ON-Resistance     | R <sub>ON2_NMOS</sub>          |                                                                        | -    | 1.3  | 2.0  | Ω    |

| VGH_LX NMOS Leakage Current   | I <sub>Leak2_NMOS</sub>        |                                                                        | -    | 10   | 20   | μA   |

| VGH_LX Maximum Duty Cycle     | D <sub>MAX_VGH</sub>           | $V_{AVDD}$ = 3.6, $V_{GH}$ = 30V,<br>$\eta$ = 0.8, $f_{OSC2}$ = 800kHz | 88.4 | 90.4 | -    | %    |

| Line Regulation               | $V_{\text{LINE}_{\text{VGH}}}$ | $V_{AVDD}$ = 3.6 to 12.7V,<br>$I_{VGH}$ = 20mA                         | -    | 0.1  | 0.15 | %/V  |

| Load Regulation               | $V_{\text{LOAD}_{\text{VGH}}}$ | I <sub>GH</sub> = 5 to 40mA                                            | -1   | -    | +1   | %    |

| Soft Start Time               | t <sub>ss_vghl</sub> -         | 2 Bits, Step = 2ms                                                     | 4    | -    | 10   | Ms   |

|                               |                                | Tolerance                                                              | -10  | -    | +10  | %    |

| LX Switch ON / OFF Slew Rate  | $TS_{VGH}$                     | 2 Bits, Step = 1.3 V/ns                                                | 2.2  | -    | 6.0  | V/ns |

| Over Voltage Protect Voltage  | V                              |                                                                        | 38   | 39   | 40   | V    |

| Over vollage Flotect vollage  | V <sub>OVP_VGH</sub>           | Hysteresis                                                             | 0.45 | 0.50 | 0.55 | V    |

| Under Voltage Protect Voltage | V                              |                                                                        | 75   | 80   | 85   | %    |

| Under vollage Protect vollage | V <sub>UVP_VGH</sub>           | $V_{VGH}$ Rising – $V_{VGH}$ Falling                                   | 0.5  | 1.0  | 1.5  | %    |

| Duration to UVP Trigger Time  | t <sub>UVP_VGH</sub>           |                                                                        | 140  | 160  | 180  | Ms   |

| Short Circuit Protect Voltage | $V_{\text{SCP}_{VGH}}$         |                                                                        | 25   | 30   | 35   | %    |

| VGHT Output Voltage Accuracy  | N/                             |                                                                        | -1   | -    | +1   | %    |

| VGHT Output Voltage Range     | – V <sub>GHT</sub>             | 5 Bits, Step = 1V                                                      | 10   | -    | 37   | V    |

| VT Source Current             | I <sub>VT</sub>                | V <sub>VT</sub> = 1V                                                   | 39   | 40   | 41   | μA   |

| VT Low Temperature Voltage    | VT_LT                          |                                                                        | -    | 0.5  | -    | V    |

| VT Low Temperature Voltage    | VT_HT                          |                                                                        | -    | 1.25 | -    | V    |

- 台灣類比科技股份有限公司 –

- Advanced Analog Technology, Inc. –

Version 0.03

Page 7 of 44

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.5V \text{ to } 5.5V, T_A = -40 \degree \text{C} \text{ to } +85 \degree \text{C}$ , unless otherwise specified. Typical values are tested at +25 °C ambient temperature,  $V_{IN} = 3.3V$ ,  $V_{AVDD} = 8.5V$ ,  $V_{GH} = 23V$ ,  $V_{GL} = -6V$ ,  $V_{25} = 2.5V$ , NAVDD = GND)

### Current Mode Buck Regulator (V25\_BUCK)

| PARAMETER                      | SYMBOL                   | TEST CONDITION                                             | MIN  | TYP   | МАХ  | UNIT |

|--------------------------------|--------------------------|------------------------------------------------------------|------|-------|------|------|

| V25 Output Voltage Accuracy    |                          |                                                            | -1   | -     | +1   | %    |

| V/25 Output Voltage Bange      | V <sub>25</sub>          | 4 Bits, Step = 0.1V                                        | 1.5  | -     | 3.0  | V    |

| V25 Output Voltage Range       |                          | 5 Bits, Step = 0.1V                                        | 1.0  | A-    | 3.0  | V    |

| V25_LX Oscillation Frequency   | f <sub>OSC_V25</sub>     |                                                            | 0.96 | 1.20  | 1.44 | MHz  |

| V25_LX Current Limit           | I <sub>LIM_ V25_LX</sub> |                                                            | 1.0  | 1.2   | 1.4  | А    |

| V25_LX NMOS ON-Resistance      | R <sub>ON3_NMOS</sub>    |                                                            |      | 80    | 100  | mΩ   |

| V25 PMOS On-Resistance         | R <sub>ON3_PMOS</sub>    |                                                            | -    | 250   | 350  | mΩ   |

| V25_LX NMOS Leakage Current    | I <sub>Leak3_MOS</sub>   |                                                            | -    | 10    | 20   | μA   |

| Line Regulation                | $V_{\text{LINE}\_V25}$   | V <sub>IN</sub> = 2.8 to 5.5V,<br>I <sub>V25</sub> = 200mA | -    | ±0.25 | ±0.5 | %/V  |

| Load Regulation                | $V_{LOAD_{V25}}$         | $V_{IN}$ = 3.3V, $I_{GH}$ = 1 to 400mA                     | —1   | -     | +1   | %    |

| Soft Start Time                | t <sub>SS3</sub>         |                                                            | 3.2  | 4.0   | 4.8  | Ms   |

| Linder Voltage Dratest Voltage | V                        |                                                            | 0.7  | 0.8   | 0.9  | V    |

| Under Voltage Protect Voltage  | $V_{UVP_V25}$            | $V_{25}$ Rising – $V_{25}$ Falling                         | 100  | 150   | 200  | mV   |

| Duration to UVP Trigger Time   | t <sub>UVP_V25</sub>     |                                                            | 140  | 160   | 180  | Ms   |

| Short Circuit Protect Voltage  | V <sub>SCP_V25</sub>     |                                                            | 0.25 | 0.30  | 0.35 | V    |

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 8 of 44

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.5V \text{ to } 5.5V, T_A = -40 \degree \text{C} \text{ to } +85 \degree \text{C}$ , unless otherwise specified. Typical values are tested at +25 °C ambient temperature,  $V_{IN} = 3.3V$ ,  $V_{AVDD} = 8.5V$ ,  $V_{GH} = 23V$ ,  $V_{GL} = -6V$ ,  $V_{25} = 2.5V$ , NAVDD = GND)

### Low Dropout Linear Regulator (V25\_LDO)

| PARAMETER                      | SYMBOL                | TEST CONDITION                                                  | MIN   | TYP  | МАХ  | UNIT |

|--------------------------------|-----------------------|-----------------------------------------------------------------|-------|------|------|------|

| Input Voltage Range            | V <sub>LDOI</sub>     |                                                                 | 2.5   | -    | 5.5  | V    |

| Output Voltage Accuracy        |                       |                                                                 | -1%   | 0    | +1%  | V    |

| Output Valtage Denge           | V <sub>25</sub>       | 4 Bits, Step = 0.1V                                             | 1.5   | A-   | 3.0  | V    |

| Output Voltage Range           |                       | 5 Bits, Step = 0.1V                                             | 1.0   | -    | 3.0  | V    |

| Dropout Voltage                | V <sub>DROP</sub>     | V <sub>IN</sub> = 3.3V, I <sub>LDO</sub> = 350mA                | ( - / | 300  | 500  | mV   |

| LDO Output Current Limit       | I <sub>lim_ldo</sub>  |                                                                 | 350   | 500  | 650  | mA   |

| Quiescent Current              | I <sub>Q_LDO</sub>    |                                                                 | -     | 60   | 100  | μA   |

| Line Regulation                | V <sub>LINE_LDO</sub> | $V_{IN}$ = 2.8 to 5.5V,<br>$V_{LDOO}$ = 2.5V, $I_{LDO}$ = 150mA | -     | 0.1  | 0.3  | %/V  |

| Load Regulation                | V <sub>LOAD_LDO</sub> | $V_{IN}$ = 3.3V, $V_{LDOO}$ = 2.5V,<br>$I_{LDO}$ = 1 to 300mA   | -     | 0.2  | 0.5  | %    |

| Linder Voltage Protect Voltage | V                     |                                                                 | 0.7   | 0.8  | 0.9  | V    |

| Under Voltage Protect Voltage  | V <sub>UVP_LDO</sub>  | $V_{LDOO}$ Rising – $V_{LDOO}$ Falling                          | 100   | 150  | 200  | mV   |

| Duration to UVP Trigger Time   | t <sub>UVP_LDO</sub>  |                                                                 | 140   | 160  | 180  | ms   |

| Short Circuit Protect Voltage  | V <sub>SCP_V25</sub>  |                                                                 | 0.25  | 0.30 | 0.35 | V    |

- 台灣類比科技股份有限公司 -- Advanced Analog Technology, Inc. -Version 0.03 Page 9 of 44

# **ELECTRICAL CHARACTERISTICS**

$(V_{\text{IN}} = 2.5\text{V to } 5.5\text{V}, \text{ } T_{\text{A}} = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are tested at } +25\,^{\circ}\text{C} \text{ ambient temperature, } V_{\text{IN}} = 3.3\text{V}, \text{ } V_{\text{AVDD}} = 8.5\text{V}, \text{ } V_{\text{GH}} = 23\text{V}, \text{ } V_{\text{GL}} = -6\text{V}, \text{ } V_{25} = 2.5\text{V}, \text{ } \text{NAVDD} = \text{GND})$

### Negative Charge Pump Regulator (for VGL)

| PARAMETER                       | SYMBOL                | TEST CONDITION                                              | MIN  | TYP | МАХ  | UNIT |

|---------------------------------|-----------------------|-------------------------------------------------------------|------|-----|------|------|

| VGL Output Voltage Accuracy     |                       |                                                             | -1   | -   | +1   | %    |

| Output Voltage Range            | V <sub>GL</sub>       | 6 Bits, Step = –0.1V                                        | -8.0 | -   | -4.5 | V    |

| DRVN Source Current             | I <sub>DRVN</sub>     |                                                             | 1    | 4   | 6    | mA   |

| Soft Start Time                 |                       | 2 Bits, Step = 2ms                                          | 4    | -   | 10   | ms   |

| Solt Start Time                 | t <sub>ss_vghL</sub>  | Tolerance                                                   | -10  |     | +10  | %    |

| Under Voltage Protect Voltage   | $V_{UVP_VGL}$         |                                                             | 75   | 80  | 85   | %    |

| Duration to UVP Trigger Time    | t <sub>UVP_BUCK</sub> |                                                             | 140  | 160 | 180  | ms   |

| Short Circuit Protect Voltage   | $V_{SCP_VGL}$         |                                                             | 25   | 30  | 35   | %    |

| Line Regulation                 | V <sub>LINE_VGL</sub> | V <sub>IN</sub> = 2.5 to 5.5V,<br>I <sub>DRVN</sub> = 0.1mA | -    | 1   | 6    | mV   |

| Effective Load Regulation Error | V <sub>LOAD_VGL</sub> | $V_{GL} = -8V$ ,<br>$I_{DRVN} = 50\mu A$ to 1mA             | -30  | -5  | -    | mV   |

### Gate Pulse Modulation (GPM)

| PARAMETER                           | SYMBOL               | TEST CONDITION                  | MIN | TYP | MAX | UNIT |

|-------------------------------------|----------------------|---------------------------------|-----|-----|-----|------|

| VFLK Input Low Voltage              | $V_{IL_VFLK}$        |                                 | -   | -   | 0.6 | V    |

| VFLK Input High Voltage             | V <sub>IH_VFLK</sub> |                                 | 1.5 | -   | -   | V    |

| VFLK Input Bias Current             | Ів4                  | V <sub>FLK</sub> = 0 to VIN_LCD | -40 | -   | +40 | nA   |

| Propagation Delay VFLK to VGHM      | tpp                  | V <sub>GH</sub> = 20V           | -   | 100 | 120 | ns   |

| VGH to VGHM Switch ON<br>Resistance | Ron_sc               |                                 | 10  | 30  | 50  | Ω    |

| RE to VGHM Switch ON Resistance     | Ron_dc               |                                 | 10  | 25  | 50  | Ω    |

| Delay Time (GPM)                    | t <sub>DLY</sub>     | 2Bits, Step = 20ms              | -   | -   | 60  | ms   |

| Delay Time Tolerance (GPM)          |                      |                                 | -10 | -   | +10 | %    |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.5V \text{ to } 5.5V, T_A = -40 \degree \text{C} \text{ to } +85 \degree \text{C}$ , unless otherwise specified. Typical values are tested at +25 °C ambient temperature,  $V_{IN} = 3.3V$ ,  $V_{AVDD} = 8.5V$ ,  $V_{GH} = 23V$ ,  $V_{GL} = -6V$ ,  $V_{25} = 2.5V$ , NAVDD = GND)

#### RESETB SYMBOL UNIT PARAMETER **TEST CONDITION** MIN TYP MAX $I_{RST} = 1.2mA$ $V_{\text{RST}}$ V **RESETB** Output Voltage 0.2 --Leakage Current $V_{RST} = 2.5V$ -1 μΑ -V 3Bits, Step = 0.2V 1.2 2.6 -**RESETB Detect Voltage** VDIV Tolerance -8 -+8 % Hysteresis V<sub>HYS\_DVI</sub> 100 150 200 mV 4 Bits, Step = 2ms 30 -0 ms **RESETB Delay Time** t<sub>RST</sub> Tolerance -10 10 % \_

#### Programmable VCOM Buffer (VCOM)

| PARAMETER                          | SYMBOL              | TEST CONDITION                                                                             | MIN  | TYP  | MAX  | UNIT |

|------------------------------------|---------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| AVDD Input Voltage Range           | V <sub>OPPI</sub>   | AVDD-NAVDD < 18V                                                                           | 3.6  | -    | 12.7 | V    |

| NAVDD Input Voltage Range          | V <sub>OPNI</sub>   | AVDD-NAVDD < 18V                                                                           | -8   | -    | -    | V    |

| VCOM Output Voltage Range          |                     | 8Bits, Step = 0.1V                                                                         | -4.1 | -    | +5.1 | V    |

| VCOM Output Voltage Accuracy       | V <sub>COM</sub>    |                                                                                            | -6   |      | +6   | LSB  |

| VCOMT Output Voltage Range         | N                   | 8Bits, Step = 0.1V                                                                         | -4.1 | -    | +5.1 | V    |

| VCOMT Output Voltage Accuracy      | . V <sub>сомт</sub> | 7                                                                                          | -6   | -    | +6   | LSB  |

| Load Regulation                    |                     | I <sub>OUT</sub> = 1 to 20mA Sourcing                                                      | -    | 1    | 2    | V/A  |

|                                    |                     | I <sub>OUT</sub> = 1 to 20mA Sinking                                                       | -    | 1    | 2    | V/A  |

| Short Circuit Current (FAVDD Type) | I <sub>SHORT</sub>  | Measure I <sub>OP_OUT</sub>                                                                | -    | ±200 | -    | mA   |

| Short Circuit Current (±AVDD Type) | I <sub>SHORT</sub>  | Measure I <sub>OP_OUT</sub>                                                                | -    | ±200 | -    | mA   |

| Slew Rate                          | SR                  |                                                                                            | 8    | 12   | -    | V/µs |

| Settling Time                      | t <sub>s</sub>      | $\pm 0.1\%$ , V <sub>OUT</sub> = 2V step,<br>A <sub>V</sub> = 1, AVDD = 5V,<br>NAVDD = -5V | -    | 500  | -    | ns   |

| Power Supply Rejection Ratio       | PSRR                | Product                                                                                    | -    | 85   | -    | dB   |

| Bandwidth                          | BW                  | –3dB                                                                                       | 12   | -    | -    | MHz  |

| Gain- Bandwidth                    |                     | Buffer Configuration                                                                       | 8    | -    | -    | MHz  |

- 台灣類比科技股份有限公司 -

- Advanced Analog Technology, Inc. -

Version 0.03

Page 11 of 44

# **ELECTRICAL CHARACTERISTICS**

$(V_{\text{IN}} = 2.5V \text{ to } 5.5V, T_{\text{A}} = -40 \,^{\circ}\text{C} \text{ to } +85 \,^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are tested at } +25 \,^{\circ}\text{C} \text{ ambient temperature, } V_{\text{IN}} = 3.3V, V_{\text{AVDD}} = 8.5V, V_{\text{GH}} = 23V, V_{\text{GL}} = -6V, V_{25} = 2.5V, \text{NAVDD} = \text{GND})$

### Operational Amplifier (2 OP)

| PARAMETER                       | SYMBOL              | TEST CONDITION                                                          | MIN      | TYP      | МАХ   | UNIT  |

|---------------------------------|---------------------|-------------------------------------------------------------------------|----------|----------|-------|-------|

| AVDD Input Voltage Range        | V <sub>OP</sub>     | AVDD-NAVDD < 18V                                                        | 3.6 0    | -        | 12.7  | V     |

| NAVDD Input Voltage Range       | V <sub>OP</sub>     | AVDD-NAVDD < 18V                                                        | -8       | 0        | 0     | V     |

| Input Supply Current            | I <sub>OP</sub>     |                                                                         | -        | 3        | -     | mA    |

| Input Offset Voltage            | V <sub>OPIN</sub>   | V <sub>CM</sub> = 0V                                                    |          | 2        | 15    | mV    |

| Average Offset Voltage Drift    |                     | $T_A = -40 \circ C$ to $+85 \circ C$                                    | ( - /    | 5        | -     | µV/°C |

| Input Bias Current              | I <sub>B_OPIN</sub> | V <sub>CM</sub> = 0V                                                    | -40      | <u> </u> | +40   | nA    |

| Input Impedance                 | RI <sub>N</sub>     |                                                                         | -        | 1        | -     | GΩ    |

| Input Capacitance               | C <sub>IN</sub>     |                                                                         | <b>-</b> | 1.35     | -     | pF    |

| Input Common mode Voltage Range | V <sub>CM</sub>     |                                                                         | -5.5     | -        | +5.5  | V     |

| Common mode Rejection Ratio     | CMRR                | $V_{OPIN} = -5.5V$ to +5.5V                                             | 50       | 80       | -     | dB    |

| Power Supply Rejection Ratio    | PSRR                |                                                                         | 60       | 70       | -     | dB    |

| Open Loop Gain                  | A <sub>VOL</sub>    | V <sub>OP_OUT</sub> = -4.5V to +4.5V                                    | 75       | 95       | -     | dB    |

| Output Swing                    | V <sub>OP_SL</sub>  | $I_{OP_OUT} = -5mA,$<br>$V_{OP_IN} = -5V$                               | -        | -4.92    | -4.85 | V     |

| 5                               | V <sub>OP_SH</sub>  | $I_{OP_OUT}$ =+5mA, $V_{OP_IN}$ = 5V                                    | 4.85     | 4.92     | -     | V     |

| Continuous Output Current       | I <sub>CONT</sub>   |                                                                         | -        | ±35      | -     | mA    |

| Short Circuit Current           | I <sub>SHORT</sub>  | Measure I <sub>OP_OUT</sub>                                             | -        | ±120     | -     | mA    |

| Slew Rate                       | SR                  | V <sub>OP_OUT</sub> = -4V to +4V,<br>20% to 80%                         | 8        | 12       | -     | V/µs  |

| Settling Time                   | t <sub>s</sub>      | ±0.1%, V <sub>OUT</sub> = 2V step,<br>AV = 1, AVDD = 5V,<br>NAVDD = -5V | -        | 500      | -     | ns    |

| Bandwidth                       | BW                  | –3dB, RL = 10kΩ,<br>CL = 10pF                                           | -        | 12       | -     | MHz   |

| Gain- Bandwidth Product         | GBPW                | RL = 10kΩ, CL = 10pF                                                    | -        | 5        | -     | MHz   |

| Phase Margin                    | PM                  | RL = 10kΩ, CL = 10pF                                                    | -        | 50       | -     | 0     |

| Channel Seperation              | CS                  | f = 5MHz                                                                | -        | 75       | -     | dB    |

# **ELECTRICAL CHARACTERISTICS**

$(V_{\text{IN}} = 2.5V \text{ to } 5.5V, T_{\text{A}} = -40 \,^{\circ}\text{C} \text{ to } +85 \,^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are tested at } +25 \,^{\circ}\text{C} \text{ ambient temperature, } V_{\text{IN}} = 3.3V, V_{\text{AVDD}} = 8.5V, V_{\text{GH}} = 23V, V_{\text{GL}} = -6V, V_{25} = 2.5V, \text{NAVDD} = \text{GND})$

### I<sup>2</sup>C Interface

| PARAMETER                                                        | SYMBOL              | TEST CONDITION          | MIN        | TYP                       | МАХ  | UNIT |

|------------------------------------------------------------------|---------------------|-------------------------|------------|---------------------------|------|------|

| SCL, SDA Input High Voltage                                      | V <sub>IH2</sub>    |                         | 1.5        | -                         | -    | V    |

| SCL, SDA Input Low Voltage                                       | V <sub>IL2</sub>    |                         | -          |                           | 0.6  | V    |

| SCL, SDA Input Capacitance                                       | C <sub>SI</sub>     |                         | -          | 5р                        | -    | F    |

| SDA Output Low Voltage                                           | V <sub>OL</sub>     | I <sub>SINK</sub> = 3mA | -          | -                         | 0.4  | V    |

| SCL Clock Frequency                                              | f <sub>OSCI2C</sub> |                         | ( - 7      | )                         | 400k | Hz   |

| SCL Clock High Period                                            | t <sub>IH3</sub>    |                         | 0.6        |                           | -    | μs   |

| SCL Clock Low Period                                             | t <sub>IL3</sub>    |                         | 1.3        | -                         | -    | μs   |

| SCL, SDA Receiving Rise Time                                     | t <sub>R1</sub>     |                         | <b>)</b> - | 20+0.1*<br>C <sub>B</sub> | 300  | ns   |

| SCL, SDA Receiving Fall Time                                     | t <sub>F1</sub>     |                         | -          | 20+0.1*<br>С <sub>в</sub> | 300  | ns   |

| I <sup>2</sup> C Data Setup Time                                 | t <sub>S1</sub>     |                         | 100        | -                         | -    | ns   |

| I <sup>2</sup> C Data Hold Time                                  | t <sub>H1</sub>     |                         | -          | -                         | 900  | ns   |

| I <sup>2</sup> C Setup Time for START Condition                  | t <sub>S2</sub>     |                         | 0.6        | -                         | -    | μs   |

| I <sup>2</sup> C Hold Time for START Condition                   | t <sub>H2</sub>     |                         | 0.6        | -                         | -    | μs   |

| I <sup>2</sup> C Bus Free Time Between STOP and START Conditions | t <sub>BUS</sub>    |                         | 4.7        | -                         | -    | μs   |

| I <sup>2</sup> C Pulse Width of Suppressed Spike                 | t <sub>PS</sub>     |                         | -          | -                         | 50   | ns   |

| I <sup>2</sup> C Bus Capacitance                                 | C <sub>B</sub>      |                         | -          | -                         | 400  | pF   |

| SDA, SCL Pull Up Resistor                                        | R <sub>PU</sub>     |                         | 4.7        | 10.0                      | -    | kΩ   |

# NVM

| PARAMETER              | SYMBOL            | TEST CONDITION | MIN | TYP   | MAX | UNIT  |

|------------------------|-------------------|----------------|-----|-------|-----|-------|

| Byte Write Time        | t <sub>BYTE</sub> |                | -   | -     | 10  | ms    |

| Byte Read Access Time  | B <sub>RT</sub>   |                | -   | 200   | -   | ns    |

| NVM Programmable Times | N <sub>NVM</sub>  |                | -   | 1,000 |     | Cycle |

Advanced Analog Technology, Inc.

November 2015

# AAT1277

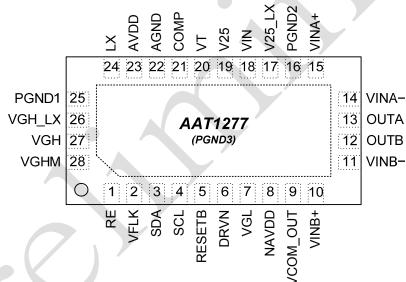

| <b>PIN DE</b> | SCRIP | <b>FION</b> |

|---------------|-------|-------------|

|---------------|-------|-------------|

| PIN NO. | NAME     | I/O | DESCRIPTION                                                                               |

|---------|----------|-----|-------------------------------------------------------------------------------------------|

| 1       | RE       | 0   | GPM Falling Time Setting Pin                                                              |

| 2       | VFLK     | 1   | GPM Control Pin (High: VGHM=VGH, Low: VGHM=Discharge)                                     |

| 3       | SDA      | I   | I <sup>2</sup> C Compatible Serial Data Input/Output                                      |

| 4       | SCL      | I   | I <sup>2</sup> C Compatible Serial Clock Input                                            |

| 5       | RESETB   | 0   | Voltage Detector Output for Resetb                                                        |

| 6       | DRVN     | 0   | Voltage Driver Output of Negative Charge Pump Linear Regulator                            |

| 7       | VGL      | I   | Output Sensing of Negative Charge Pump Linear Regulator                                   |

| 8       | NAVDD    | I   | Negative Input of VCOM and Operational Amplifiers                                         |

| 9       | VCOM_OUT | 0   | VCOM Buffer Output                                                                        |

| 10      | VINB+    | I   | Non-Inverting Input of Operational Amplifier B                                            |

| 11      | VINB-    | I   | Inverting Input of Operational Amplifier B                                                |

| 12      | OUTB     | 0   | Operational Amplifier B Output                                                            |

| 13      | OUTA     | 0   | Operational Amplifier A Output                                                            |

| 14      | VINA-    | I   | Inverting Input of Operational Amplifier A                                                |

| 15      | VINA+    | I   | Non-Inverting Input of Operational Amplifier A                                            |

| 16      | PGND2    | -   | Power Ground for Buck Regulator                                                           |

| 17      | V25_LX   | 0   | Switch Node of Buck Regulator or LDO                                                      |

| 18      | VIN      | I   | Power Supply Input                                                                        |

| 19      | V25      | I   | Output Sensing of Buck Regulator or LDO                                                   |

| 20      | VT       | 0   | Negative Temperature Compensation Pin for VGH and VCOM                                    |

| 21      | COMP     | 0   | Compensation Pin for AVDD Boost Regulator                                                 |

| 22      | AGND     | -   | Analog Ground                                                                             |

| 23      | AVDD     |     | Output Sensing of AVDD Boost Regulator, Positive Input of VCOM and Operational Amplifiers |

| 24      | LX       | 0   | Switch Node of AVDD Boost Regulator                                                       |

| 25      | PGND1    | -   | Power Ground for VGH Regulator                                                            |

| 26      | VGH_LX   | 0   | Switch Node of VGH_LX Boost Regulator                                                     |

| 27      | VGH      | I   | Output Sensing of VGH Boost Regulator                                                     |

| 28      | VGHM     | 0   | Gate Pulse Modulation (GPM) Output                                                        |

| 29      | PGND3    | -   | Power Ground for AVDD Regulator                                                           |

- 台灣類比科技股份有限公司 -

- Advanced Analog Technology, Inc. -

Version 0.03

Page 14 of 44

# **FUNCTIONAL BLOCK DIAGRAM**

- 台灣類比科技股份有限公司 -

Advanced Analog Technology, Inc. –

Version 0.03

Page 15 of 44

Advanced Analog Technology, Inc.

## **THEORY OF OPERATION**

The AAT1277 offers a complete solution for powering TFT LCD panels. The device integrates two current mode boost regulators, one synchronous boost regulator for the source driver supply, and the second non-synchronous boost regulator with temperature compensation to generate a gate-on voltage for VGH. The AAT1277 also includes a negative charge pump linear regulator for the gate-off voltage, a synchronous buck regulator or a low dropout linear regulator alternatively for system logic power, a gate pulse modulation (GPM) for improving TFT LCD image quality, a XON reset function for input supply monitor, a unity-gain Buffer for VCOM calibrator and two operational amplifiers in the device. The device includes various system protection schemes such as soft start, power up sequencing, fault protection, and thermal shutdown. The AAT1277 also includes I<sup>2</sup>C interface for various device settings such as output voltages, switching frequency, soft start time, delay time, etc.

#### Under Voltage Lockout (UVLO)

For systematic startup, AAT1277 employs a UVLO rising threshold of 2.35V typical. Thus, the input supply must exceed the UVLO threshold for the regulators to begin switching. Likewise, the device shuts down all functions when the input voltage is lower than UVLO falling threshold of 2.20V. A 150mV hysteresis is added to prevent device chattering when the input supply is noisy or unstable during power up or power down.

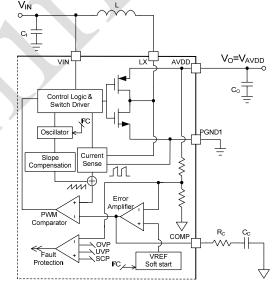

#### **Boost Regulator for AVDD**

The synchronous AVDD boost converter integrates a low  $R_{DSON}$  (typical 0.2 $\Omega$ ) NMOS for the low side switch, and a PMOS as the output rectifier. The boost output voltage, over current protection (OCP) threshold, soft start time, switching ON/OFF transient slew rate, and switching frequency are programmed via I<sup>2</sup>C interface.

The output voltage can be set from 3.6V to 12.7V with a step resolution of 0.1V. Over current protection (OCP) threshold ranges from 1A to 2A with 1A steps, soft start

## AAT1277

time can be set from 20ms to 80ms with 20ms steps, and the LX switching ON/OFF transient slew rate can be set from 0.5V/ns to 1.1V/ns with 0.2V/ns steps. The LX switching frequency can be programmed for either 600kHz, 800kHz, 1000kHz, or 1.2MHz. The boost regulator operates from a minimum input voltage of 2.5V, and delivers an output voltage that reaches the maximum capable duty cycle. The duty cycle (D) is calculated by

$$D = \frac{V_O - V_I}{V_O}$$

or  $\frac{V_O}{V_I} = \frac{1}{1 - D}$

where  $V_O$  ( $V_{AVDD}$ ) is the output of the boost regulator. Typical maximum duty cycle is approximately 80%.

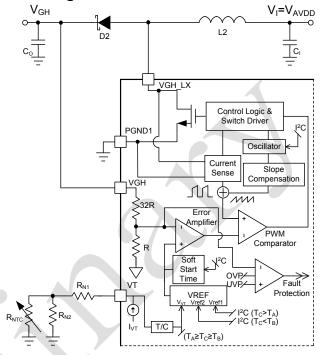

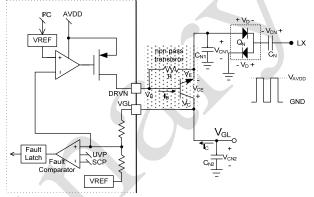

At the heart of the current mode topology are two feedback loops. See the AVDD Boost Regulator Functional Block Diagram Figure 1.

#### Figure 1. AVDD Boost Regulator Functional Block Diagram

One feedback loop generates a ramp voltage as the inductor current flows through the on resistance of the internal low side power switch. The second loop monitors the boost output via an internal feedback. This feedback voltage is compared to an internal reference voltage using a transconductance error amp. Note that the internal reference voltage is adjusted via I<sup>2</sup>C control to set the output voltage.

Regulation is achieved by modulating the internal low

Page 16 of 44

Version 0.03

side power switch (NMOS) ON time. During the ON time, the low side NMOS is turned ON to energize the inductor while the high side power switch (PMOS) rectifier is turned OFF. When the NMOS turns off, the PMOS rectifier will turn ON, releasing the inductor energy to regulate the output. The modulating duty cycle is determined by comparing the error amplifier output to the voltage ramp at the non-inverting input of the PWM comparator. Note that this voltage ramp is the sum of the signals generated by the inductor current sense circuitry and the slope compensation circuitry. Slope compensation is added to prevent sub-harmonic oscillations for duty cycles above 50%. During each rising edge of the internal clock pulse, the low side power switch is turned on. The switch is turned off when the voltage ramp generated at the non-inverting input of the PWM comparator exceeds the output voltage of the error amplifier or the voltage at the inverting input of the PWM comparator.

#### Over Voltage Protection (OVP) for AVDD

When the AVDD boost output exceeds its Over Voltage Protection threshold (typical 15V), the AAT1277 disables the gate driver of this boost regulator and prevents the internal NMOS from switching. Once AVDD voltage falls below the OVP threshold with a hysteresis of approximately 1.25V, the boost will resume switching.

#### Under Voltage Protection (UVP) for AVDD

When AVDD output voltage drops below its under voltage protection threshold (80% of programmable output voltage) due to overload conditions, an internal fault timer of 160ms is activated. Once activated, if the fault condition surpasses the 160ms, the device will be shutdown. To restart the device, the  $V_{IN}$  power must be recycled below the UVLO falling threshold.

#### Short Circuit Protection (SCP) for AVDD

When AVDD output voltage drops below its short circuit protection threshold (30% of programmable output voltage) due to short circuit conditions, the device will immediately shutdown. This latched condition is reset by toggling  $V_{\rm IN}$  power.

### Boost Regulator for VGH

### Figure 2. VGH Boost Regulator Functional Block Diagram

The non-synchronous boost regulator that supplies the VGH voltage to the TFT-LCD gate-on voltage also uses a current mode control scheme. Similarly, the output voltage is programmed via I<sup>2</sup>C interface, and can be set from 10V to 37V with 1V step resolution. The switching frequency of the VGH boost can be set to 400kHz or 800kHz with 400kHz steps and the LX switching ON/OFF transient slew rate can be set from 2.2V/ns to 6.0V/ns with 1.3V/ns steps. The soft start time can be programmed from 4ms to 10ms using 2ms steps.

### OVP & UVP for VGH

The VGH boost regulator also includes OVP and UVP. Both protection mechanisms are the same as for AVDD boost regulator, specifically 80% of VGH for UVP and typical 39V of VGH for OVP. UVP has a 160ms delay time to ensure a true UVP condition and a triggered condition latches the device, which can only be reset by recycling VIN power.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 17 of 44

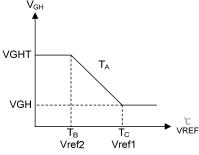

#### **VGH Temperature Compensation**

The voltage (V<sub>NTC</sub>) at VT Pin will adjust the reference voltage at the non-inverting input of the error amplifier. This reference voltage will also adjust the VGH regulation voltage, and therefore tune the output voltage (V<sub>GH</sub>). The output voltage (V<sub>GH</sub>) is compensated accordingly. For conditions where the temperature is  $T_B \leq T_A \leq T_C$ , as show in the temperature compensation for VGH Figure 3, the reference or voltage at NTC is dependent on the voltage (V<sub>NTC</sub>) at the VT Pin via the following equation:

Figure 3. Temperature Compensation for VGH

$V_{NTC} = I_{NTC} \times \left( R_{N2} + \frac{R_{N1} + R_{NTC}}{R_{N1} \times R_{NTC}} \right)$

Thus, the output voltage  $V_{GH}$  will be  $V_{GH} = k \times V_{NTC}$

where k = 33 is the internal resistive voltage divider ratio at the non-inverting input of the error amplifier,

If the ambient temperature  $T_A$  is below  $T_B$ , the  $V_{GH}$  voltage will be VGHT, which is set via  $I^2C$  and can be set from 25V to 39V with a 1V resolution. Likewise, if  $T_A$  is above  $T_C$ , the reference generated will be Vref1, and the  $V_{GH}$  voltage will be again dependent on the  $I^2C$  setting for a range of 15V to 35V. The conditions and equations that determine the  $V_{GH}$  voltage are summarized in Table 1.

| Table | 1 |

|-------|---|

| IUNIC |   |

| \v<br>V<br>V | $T_A < T_B$                       | $T_B{\leq}T_A{\leq}T_C$                              | $T_A \! > \! T_C$                |

|--------------|-----------------------------------|------------------------------------------------------|----------------------------------|

| VREF         | Vref2                             | V <sub>VT</sub>                                      | Vref1                            |

| VGH          | VGHT,<br>I <sup>2</sup> C Setting | Dependent on<br>external R <sub>NTC</sub><br>network | VGH,<br>I <sup>2</sup> C Setting |

## V25 Voltage Selection

The V25 Voltage could be supplied either by the Buck regulator, or LDO determined by the state of BUCK or LDO configuration bit in the CONFIG register.

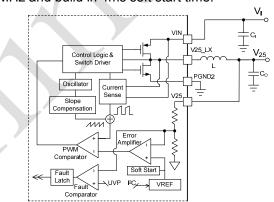

#### **Buck Regulator for V25**

The buck regulator includes a high-side PMOS and a low-side NMOS which eliminate the need for an external Schottky diode. Low on-resistance for both the switches maximizes efficiency. Moreover, the buck is compensated internally so that no external compensation network is required.

The buck output voltage is programmed via  $I^2C$  interface, and can be set from 1.5V to 3.0V with 0.1V step resolution. It operates at a fixed switching frequency of 1.2MHz and build in 4ms soft start time.

#### Figure 3. V25 Buck Regulator Functional Block Diagram

The buck regulator also uses the peak current mode PWM control scheme for fast transient response and cycle-by-cycle current limiting. The PWM maintains a constant frequency and varies the duty ratio according to the output voltage and load current. This modulation scheme provides high efficiency at medium to heavy load conditions, and reduces the output ripple at light load conditions. It regulates output voltage from V<sub>IN</sub> down to an output voltage as low as 1.5V (1.0V). The duty cycle D is calculated by

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}}}{\mathsf{V}_{\mathsf{I}}} \quad (\mathsf{V}_{\mathsf{O}} = \mathsf{V}_{25})$$

where  $V_{\rm O}$   $(V_{25})$  is the output voltage of the buck regulator.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 18 of 44

#### Buck Current Limit

The buck regulator includes cycle by cycle current limiting, with a threshold of typically 1.2A. When the current limit threshold is reached, the high side PMOS switch is turned off, releasing the inductive energy.

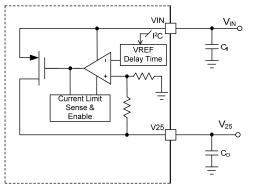

#### LDO for V25

The integrated LDO output voltage can be programmed form 1.5V to 3.0V via V25 register and the LDO starts as soon as the supply voltage exceeds the UVLO threshold with 4ms soft-start time, the same time as the buck regulator. The LDO is capable of a minimum 350mA output load.

Figure4. V25 LDO Function Block Diagram

#### UVP for V25

The Buck regulator also includes UVP protection mechanisms. When the buck output drops below the Under Voltage Protection threshold (typical 0.8V), an internal fault timer counter is activated. Once the fault condition surpasses 160ms, the buck and other regulators will be shutdown. To restart the device, the VIN power must be recycled below the UVLO falling threshold.

# Negative Charge Pump Linear Regulator for VGL

The AAT1277 integrates a Charge pump controller which drives an external NPN pass transistor to form a linear regulator that receives an input voltage provided by the charge pump, and generates a linear negative supply for the TFT LCD panel gate-off voltage. For the linear regulator to deliver the required output voltage and current, an base-to-emitter resistance  $(6.8k\Omega)$  for AAT1277

external NPN pass transistor guarantes a base-drive current. The maximum output voltage capability is determined by the number of charge pump stage, but the actual regulated output voltage is set via  $I^2C$  interface. Using a 6 bit resolution, the VGL voltage can be set from -8.0V to -4.5V with 0.1 steps. Typical application uses a single stage, as shown in Figure 5.

#### Figure 5. Negative Charge Pump Linear Regulator Functional Block Diagram

When the LX is High ( $V_{AVDD}$ ), the flying capacitor  $C_N$  will charge as the lower diode will turn on and create a path to ground, and  $V_{CN}+V_D=V_{AVDD}$ . When the LX is Low (GND), the flying capacitor  $C_N$  is level shifted in the negative direction, and the node connecting between  $C_N$ and  $Q_N$  becomes ( $-V_{CN}$ ). Thus, charge will flow from the output  $C_{N2}$  to  $C_N$  by through the external NPN pass transistor, and the output can be expressed as

$(-V_{CN})=V_{CN2}-V_{CE}-V_{D} \rightarrow V_{CN2}=(-V_{CN}) + V_{CE} + V_{D}$  $V_{CN2}=(-V_{AVDD})+2V_{D}+V_{CE}$

The voltage magnitude of V<sub>CE</sub> is controlled by the drive strength of DRVN, which is a p-channel open-drain output. When the NPN pass transistor is fully turned ON, the maximum capable output of this single stage charge pump is approximately  $V_{GL}=V_{CN2}=(-V_{AVDD})+0.8V$

where V<sub>CE</sub>≈0.2V, V<sub>D</sub>≈0.3V.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 19 of 44

#### **NPN PASS Transistor**

For the linear regulator to deliver the required output voltage and current, the NPN transistor must be properly selected. The transistor's current gain ( $h_{FE}$ ) limits the guaranteed maximum output current  $I_C$  to:

$$I_{C} = h_{FE} \times (I_{B} - \frac{V_{BE}}{R_{BE}})$$

where  $I_B$  is the base current,  $V_{BE}$  is the bass-to-emitter forward voltage drop, and  $R_{BE}$  is the pull-up resistor connected between the transistor's base and emitter. Note that too high of a transistor current gain can destabilize the linear regulator output due to a high loop gain. For the AAT1277, the bias current of the negative linear regulator controller is 0.1mA, therefore, the base-to-emitter resistor should be

$\mathsf{R}_{\mathsf{BE}} = \frac{\mathsf{V}_{\mathsf{BE}}}{0.1 \mathrm{mA}} = \frac{0.7 \mathrm{V}}{0.1 \mathrm{mA}} \gg 6.8 \mathrm{k}\Omega$

This should provide an output current of at least 50mA.

Other factors such as the transistor saturation voltage at maximum output load current and maximum power dissipation rating of the transistor must be considered when selecting the proper NPN pass transistor.

#### **Charge Pump Flying Capacitors**

Use a  $0.1\mu$ F ~  $0.47\mu$ F for the flying capacitor (C<sub>N</sub>) and make sure that the voltage rating (V<sub>CN</sub>) of the capacitor is adequate per the number of stages. The voltage rating of the capacitor must satisfy

#### V<sub>CN</sub>>n x V<sub>AVDD</sub>

Where  $V_{AVDD}$  is the input supply to the charge pumps, and n is the number of stages per charge pump. Note that the negative charge pump uses 1 stage, i.e. n = 1.

### **Output Capacitor**

The output capacitor of the linear regulator affects the stability of the regulator. To ensure stability, choose an output capacitor in the range of  $1\mu$ F ~  $4.7\mu$ F, with low ESR.

### Gate Pulse Modulation (GPM)

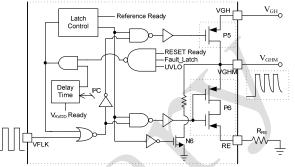

An internal high voltage switch controller is included for gate pulse modulation which provides gate shaping to improve image quality in TFT LCD applications. The circuitry consist of two high voltage PMOS, one between VGH and VGHM, and another between VGHM and RE. See Figure 6 for the Gate Pulse Modulation Functional Block Diagram.

#### Figure 6. Gate Pulse Modulation Functional Block Diagram

When the switch controller is enabled, logic level on the VFLK input will determine which PMOS switch is ON or OFF. If VFLK is logic High, P5 turns on and P6 turns off, VGHM connects to VGH. If VFLK is logic Low, P5 turns off and P6 turns on, VGHM connects to RE, and the VGHM output ( $V_{GHM}$ ) is discharged via the resistor connected at RE to ground. Note that the resistor ( $R_{RE}$ ) value can be adjusted to different discharge time or high to low transient slope rate.

The GPM is enabled only after a set of power ready condition is present. For the GPM to be enabled, the device supply voltage should exceed the UVLO threshold, RESET function must be power on ready, no fault condition is present, and the programmable delayed time,  $t_{DLY}$  range from 0ms to 80ms with 20ms step resolution, should have passed after V<sub>GH</sub> soft start has completed. Note that during the GPM enable period, VGH output will be internally pulled to ground via an internal resistor and NMOS (N6). Once enabled, VFLK input will control the internal switches.

During operation, if the input supply falls below the UVLO threshold, the GPM will be immediately disabled. Instantly, the high side PMOS P5 will turn on, the low side PMOS P6 will turn off simultaneously, and VFLK input will have no control over the PMOS switches.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 20 of 44

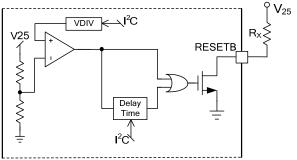

#### **RESETB (XAO)**

This device has an internal reset circuit to monitor the voltage at V25. When V25 is lower than the detect threshold VDIV, RESET output will be pulled low. RESETB is an open-drain output that needs a pull-up resistor ( $R_x = 10k\Omega$ ) to a system supply. The VDIV is set via I<sup>2</sup>C from 1.2V to 2.6V with 0.2V step resolution. In typical application, see Figure 7 for RESETB Functional Block Diagram.

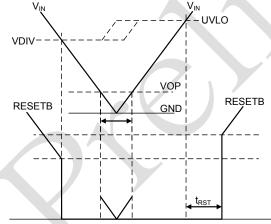

When V25 rises above its UVLO threshold (2.35V typ.),  $V_{HYS\_DIVI}$ , after V25 had finished ramp, the output will be pulled High after  $t_{RST}$  delay time has completed. The  $t_{RST}$  delay time ranges from 0ms to 30ms with 2ms step resolution and also can be set via  $I^2C$ . See Figure 8 for RESETB Operation Timing Chart

Figure 8. RESETB Operation Timing Chart

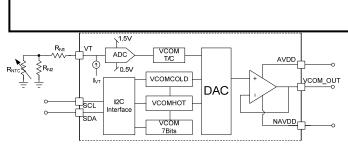

#### Programmable VCOM Buffer

The I<sup>2</sup>C programmable VCOM operation amplifier can be used to digitally adjust a panel's VCOM voltage to remove flicker.

AAT1277

The VCOM voltage calibration needs two steps for adjustment. First step is to set the central value of VCOM voltage according to the  $V_{AVDD}$ ,  $V_{GH}$ , and LCD panel characteristic. The VCOM voltage is programmable from 0.8V to 5.1V or -4.1V to +0.2V by VCOM register. The first step is normally done in PCB assembly manufacture.

Second step is to calibrate the VCOM voltage on the LCD panel assembly line by VCOM RAM register through I<sup>2</sup>C digital interface. The VCOM register value indicates the voltage increment or decrement of VCOM\_OUT which is preset by V<sub>COM</sub>. Once the proper value is identified, the V<sub>COM</sub> register value can be renewed with VCOM register value added. The default value for VCOM register is 1,000,000. If 100,0001 is written into VCOM register, the V<sub>COM</sub> value will increase with one DAC step. In the other hand if 0111,111 is written to VCOM register, the V<sub>COM</sub> will decrease with one DAC step.

The VCOM voltage also supports temperature compensation and allows its output voltage to transition from a lower voltage at low temperatures V<sub>COMT</sub> to a higher voltage at high temperatures V<sub>COM</sub>. The output voltage with temperature compensation is decided by voltage at the VT pin. The thermistor network formed by R1, R2, and RNTC generates a voltage at the VT pin whose value decreases with increasing temperature. With proper selection of the external components RNTC, R1, and R2, temperatures THOT and TCOLD can be configured to suit each display's characteristics. The temperature compensation resolution is 6 Bits. The temperature compensation for VCOM could be turn on/off by bit VCOMT in register CONFIG. If temperature compensation for VCOM is ON state, both  $V_{COM}$  and  $V_{COMT}$  need to be input. Otherwise only  $V_{COM}$  is active for VCOM voltage setting without temperature compensation.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 21 of 44

Advanced Analog Technology, Inc.

**Figure 9. PVCOM Function Block**

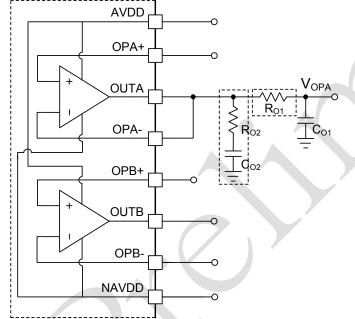

#### **Operational Amplifiers**

There are two operational amplifiers in the device. Both of them are capable of rail-to-rail input and output, ±120mA output short-circuit current, and a 12V/µs slew rate. The positive and negative supplies of operational amplifiers are connected to the AVDD pin and NAVDD pin individually. For minimize the power consumption, setting the OPA\_A bit or OPA\_B bit in CONFIG register can turn on or off operational amplifier individually.

Figure 10. Operational Amplifier Functional Block Diagram

In the unity-gain configuration, the capacitive load adds a pole to the loop gain that impacts the stability of the system and leads to output peaking, ringing and oscillation. A higher pole frequency results in greater stability. In fact, if the pole frequency is lower than or close to the unity gain frequency, the pole can have a significant negative impact on phase and gain margins.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 22 of 44

AAT1277

Therefore, the stability decreases when the capacitive load increases.

One method of improving capacitive load drive is to insert a  $2\Omega$  to  $20\Omega$  resistor (R<sub>01</sub>) in series with the output, as shown in Figure 6. This reduces ringing with large capacitive loads while maintaining DC accuracy.

Another method for improving transient response is to add a snubber circuit at the output. A snubber circuit consists of a resistor ( $R_{O2}$ ) in series with a capacitor ( $C_{O2}$ ), which improves output settling time and reduces peaking. The advantage of this topology is that it draws no DC current nor does it reduce the gain.

#### **Thermal Shutdown**

The AAT1277 device enters into fault protection shutdown when the junction temperature reaches approximately 150°C. To restart the device when the junction temperature has fallen below the thermal shutdown threshold, recycle the device supply power below the UVLO falling threshold.

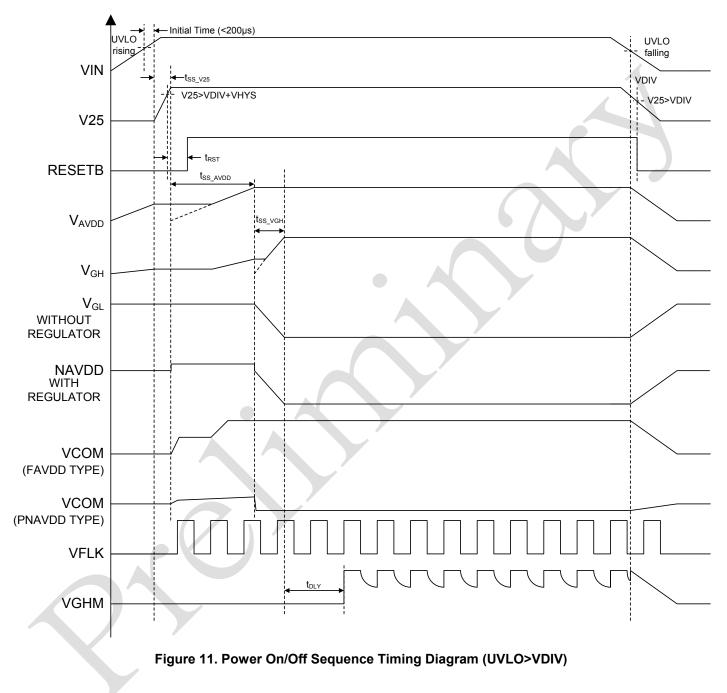

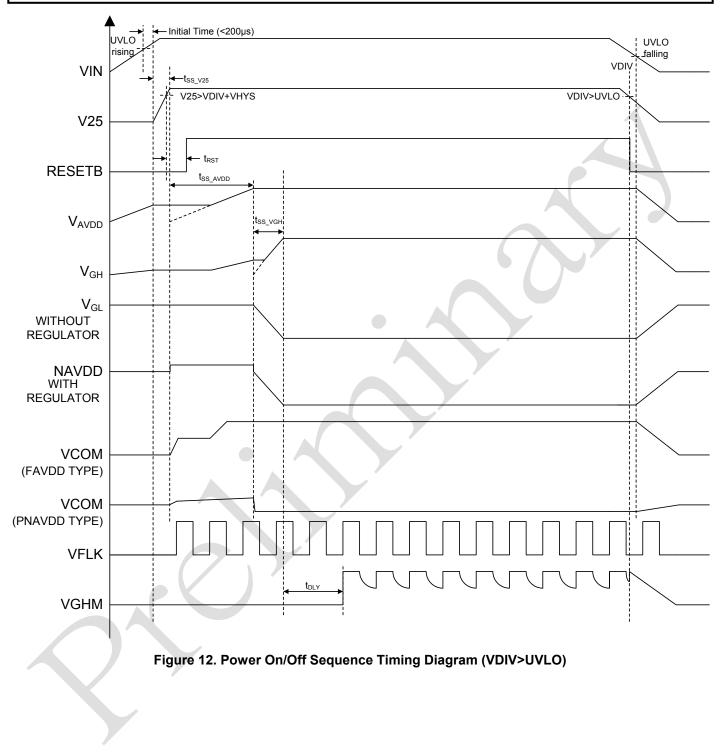

### Power On/Off Sequence

The AAT1277 Power On/Off Sequence is as shown in Figure 11 and Figure 12.

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 23 of 44

Advanced Analog Technology, Inc.

## AAT1277

#### I<sup>2</sup>C Serial Interface

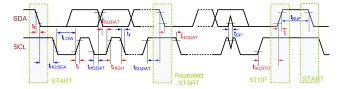

The AAT1277 features an  $I^2C$ -compatible, 2-wire serial interface consisting of a SDA and a SCL. SDA and SCL are an I/O with an open-drain output that requires a pull up resistor to realize high-logic levels. Pull up resistor values should be chosen to ensure that the rise and fall times are within specification. A typical value for the pull up resistors is 4.7k $\Omega$ . Each slave on the  $I^2C$  bus responds to a slave address byte sent immediately following a Start Condition. Below diagram shows the definition of timing on  $I^2C$  bus:

Figure 13. Definition of timing on I<sup>2</sup>C bus

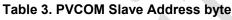

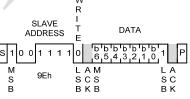

The slave address byte contains the slave address in the most significant 7 bits and the R/W bit in the least significant bit. The AAT1277 consist of two slave addresses, one slave address for accessing the PVCOM, the other slave address for accessing the PMIC section (Power Management Integrated Circuit). Below diagram shows the two slave addresses:

| 1                               | 0 | 0 | 1 | 1 | 1 | 7 | R/W |

|---------------------------------|---|---|---|---|---|---|-----|

| MSB                             |   |   |   |   |   |   | LSB |

| Table 4 PMIC Slave Address byte |   |   |   |   |   |   |     |

| 1                               | 1 | 1 | 0 | 1 | 0 | 0 | R/W |

| MSB                             |   |   |   |   |   |   | LSB |

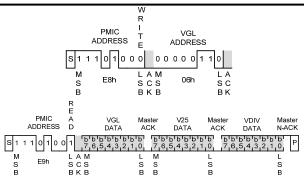

### I<sup>2</sup>C Protocol for PVCOM

When the R/W bit is 0 (such as in 9Eh), the master is indicating it will write data to the slave. If R/W = 1 (9Fh in this case), the master is indicating it wants to read from the slave. During an I2C write operation, the master must transmit a register address to identify the memory location where the slave is to store the data.

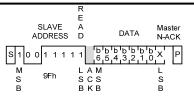

A master device writes data to DR (DAC Register) by the following timing diagram.

A master device writes data to DR (DAC Register) and EE (EEPROM) by the following timing diagram.

|             | SLAVE<br>DDRESS | I<br>T<br>E             | DATA                       |

|-------------|-----------------|-------------------------|----------------------------|

| S 1 0 0     | 1 1 1           | 10 <sup>bb</sup><br>65  | b'b'b'b'b<br>4,3,2,1,0,0 P |

| M<br>S<br>B | 9Eh             | L A M<br>S C S<br>B K B | L A<br>S C<br>B K          |

A master reading data from EE by the following timing diagram: (then DR = EE)

- 台灣類比科技股份有限公司 –

Advanced Analog Technology, Inc. –

Version 0.03

Page 25 of 44

Advanced Analog Technology, Inc.

AAT1277

S: Start Condition, P: Stop Condition, X : Don't Care.

□: Master to Slave, □:Slave to Master

### I<sup>2</sup>C Protocol for PMIC

When the R/W bit is 0 (such as in E8h), the master is indicating it will write data to the slave. If R/W = 1 (E9h in this case), the master is indicating it wants to read from the slave. During an I2C write operation, the master must transmit a register address to identify the memory location where the slave is to store the data. The register address is always the second byte transmitted during a write operation following the slave address byte. The AAT1277 PMIC register addresses refer to the I2C register map.

During power-up, the values stored in the EE (EEPROM, nonvolatile memory) are recalled into the DR (DAC Register, volatile memory).

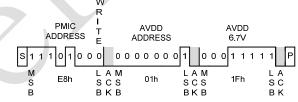

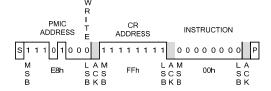

#### WRITE OPERATION

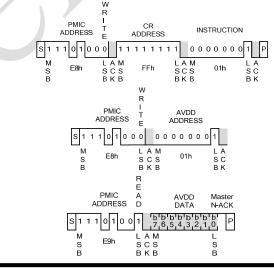

#### Write Single Byte To DR (DAC Register):

- Step 1: Master sends Start Condition.

- Step 2: Master sends the value E8h. (the AAT1277 PMIC address 1110100b and R/W bit = Low) AAT1277 will acknowledge a bit for this byte.

- Step 3: Send DR address (ex.01h, address of AVDD)

- AAT1277 will acknowledge a bit for this byte.

- Step 4: Send the data to be written to the DR (ex.1Fh, VCC = 6.7V) AAT1277 will acknowledge a bit for this byte.

- Step 5: Master sends Stop Condition.

- Example: Writing 1Fh (6.7V) to the DR address 01h (AVDD)

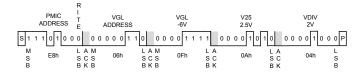

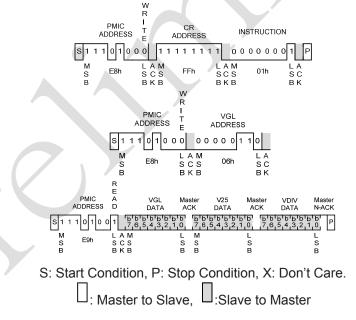

### Write Multiple Bytes To DR (DAC Register):

- Step 1: Master sends Start Condition.

- Step 2: Master sends the value E8h. (The AAT1277 PMIC address 1110100b and R/W bit = Low) AAT1277 will acknowledge a bit for this byte.

- Step 3: Send DR address (ex.06h, address of VGL)

- AAT1277 will acknowledge a bit for this byte.

- Step 4: Send the data to be written to the DR (ex.0Fh, VGL=-6V) AAT1277 will acknowledge a bit for this byte.

- Step 5: Master continues sending the other bytes to be written to the DRs. AAT1277 will acknowledge a bit for each byte and DR address will automatically increase.

- 台灣類比科技股份有限公司 Advanced Analog Technology, Inc. -

Version 0.03

Page 26 of 44

#### Step 6: Master sends Stop Condition.

Example: Writing 0Fh(-6V), 0Ah(2.5V), 04h(2V) to the DR address 06h, 07h, 08h (VGL, V25, VDIV)

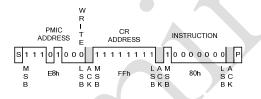

#### Write All DR (DAC Register) Data To EE (EEPROM):

- Step 1: Master sends Start Condition.

- Step 2: Master sends the value E8h. (the AAT1277 PMIC address 1110100b and R/W bit = Low) AAT1277 will acknowledge a bit for this byte.

- Step 3: Send CR (Control Register) address (FFh)

AAT1277 will acknowledge a bit for this byte.

- Step 4: Send the instruction 1000000b (X: Don't care, ex. 80h) to make duplicate data from DR to EE. AAT1277 will acknowledge a bit for this byte.

- Step 5: Master sends Stop Condition.

- Example: Writing all DR data to EE.

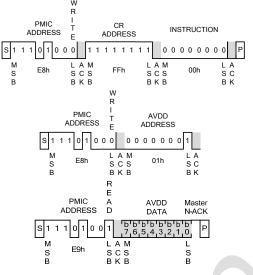

#### **READ OPERATION**

#### Read Single Data From DAC Register (DR):

- Step 1: Master sends Start Condition.

- Step 2: Master sends the value E8h. (the AAT1277 PMIC address 1110100b and R/W bit = Low) AAT1277 will acknowledge a bit for this byte.

- Step 3: Send Control Register (CR) address (FFh) AAT1277 will acknowledge a bit for this byte.

- Step 4: Send the instruction 0000000b (X: Don't care, ex. 00h) to specify that the data is read from the DR. AAT1277 will acknowledge a bit for this byte.

- Step 5: Master sends Stop Condition.

- Step 6: Master sends Start Condition.

- Step 7: Master sends the value E8h. (The AAT1277 PMIC address 1110100b and R/W bit = Low) AAT1277 will acknowledge a bit for this byte.

- Step 8: Send specified DR address to be read (ex.05h, address of AVDD) AAT1277 will acknowledge a bit for this byte.

- Step 9: Master sends Start Condition (Repeated Start Condition, instead of Stop Condition)

- Step 10: Master sends the value E9h. (the AAT1277 PMIC address 1110100b and R/W bit = High) AAT1277 will acknowledge a bit for this byte.

- Step 11: Master read the data from DR and not-acknowledges for this byte.

- Step 12: Master sends Stop Condition.